Hi,

I read a article from this http://www.ti.com/lit/an/slyt559/slyt559.pdf.

This article is about when the JESD204B is better choice than parallel LVDS. I just want to extend this topic into more depth.

As far as I know, JESD204B has huge advantage over parallel LDVS in the system implementation for great number of channels. This is because the SerDes reduces the pins and layout traces and recovers the clock in RX end. Hence, the cost of data aligning between devices could be reduced dramatically in the system with great number of channels.

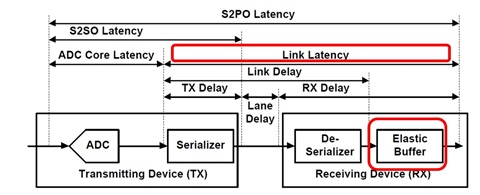

But the SerDes also introduces the variability in the latency across the link because of the following statement from section 1.3 in 'Minimizing Delay Uncertainty in Radio Equipment Using JESD204B'

Recovered word alignment and phase offset between recovered clock and local clock make the delays associated with SerDes interfaces variable and subject to change upon each startup.

So additional alignment method such as using elastic buffer is used in JESD204B to meet the phase alignment requirement in some application such as MIMO and phased array.

Hence, the latency is increased although it's deterministic in JESD204B.

Actually, I am designing one automotive RADAR target echo simulator. It will receive the signal from the automotive RADAR and add some delay and Doppler frequency and then re-transmit the modified signal back to the automotive RADAR to simulate multiple targets.

In my application, the system processing latency is one key parameter to decide the minimum distance from automotive RADAR.

So I am choosing the ADCs/DACs carefully not to introduce more additional latency. From this http://www.ti.com/lit/an/slyt559/slyt559.pdf, I got following

So it seems better if I choose the ADCs/DACs with LVDS for minimum latency consideration.

But I have some questions still.

1. What's the typical value of S2PO latency of the ADCs/DACs with JESD204B? Tens of ns? Hundreds of ns?

I find the value of latency of the ADCs/DACs with LVDS could be less than 10 ns.

2. I think the latency value of ADCs/DACs with JESD204B could be very larger than that with LVDS. Why? Does the Serializer or De-serializer or the elastic buffer introduce the huge additional latency?

3. Is the latency of ADCs/DACs with LVDS deterministic?

Regards,

Feng