Part Number: AFE5851

Hi,

I'm using AFE5851 with an FPGA from Xilinx (Kintex 7). The clock frequency for the ADC is 62.5 MHz, thus frame clock frequency is 31.25 MHz. Deserialization is implemented by IDELAYE2 and ISERDESE2 primitives in 12 bit mode.

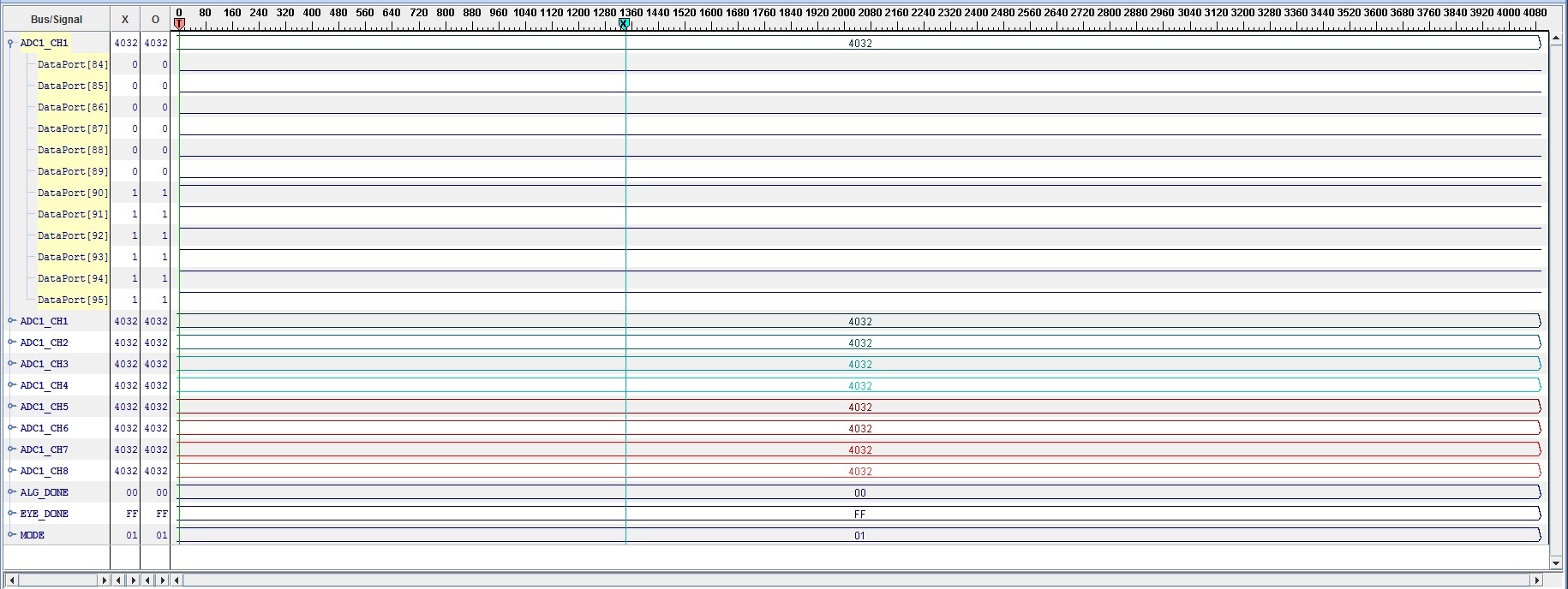

I use the deskew pattern to tune the 8 serial data lanes of the AFE5851. This works fine as shown in in the figure below:

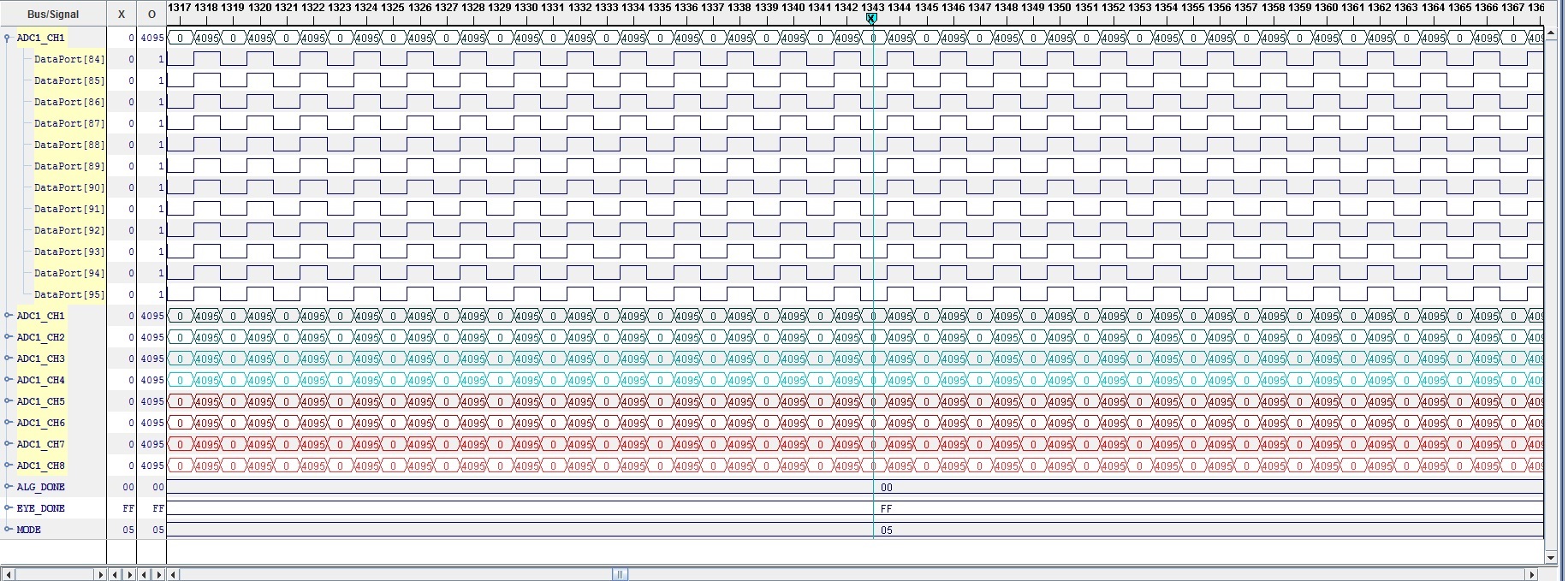

After that, the sync pattern is used to align 12-bit data words. This also works fine:

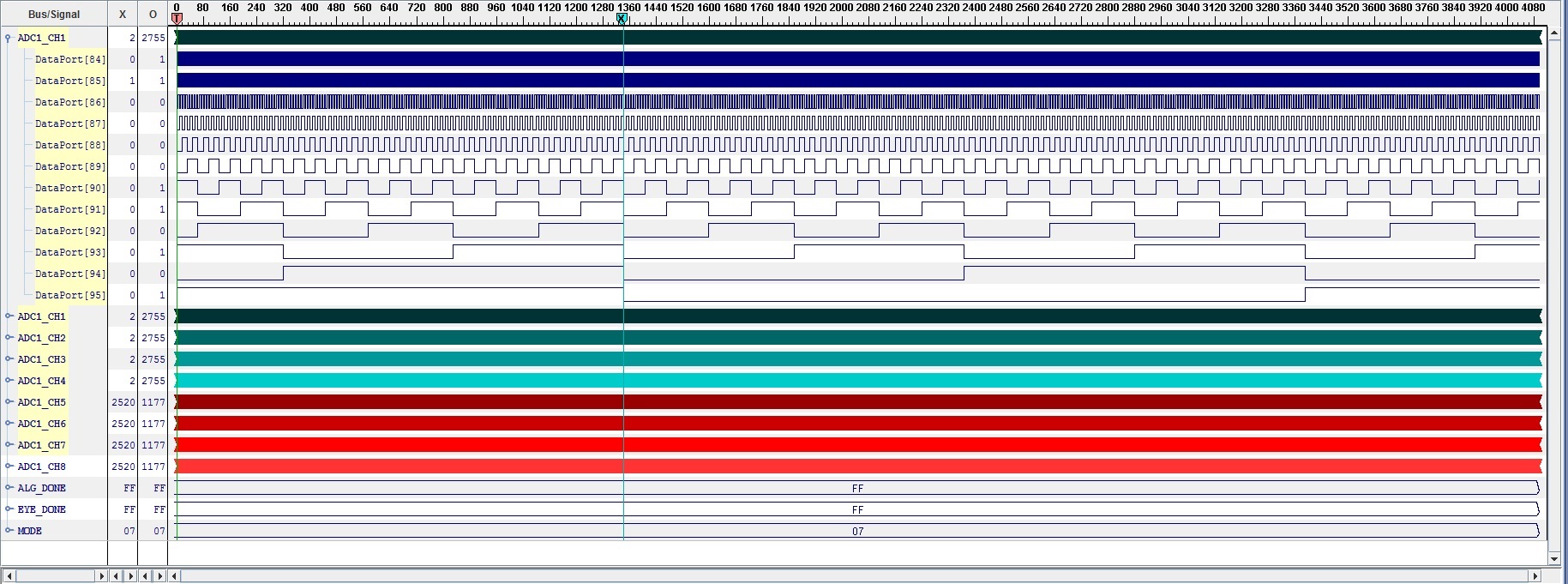

To check word alignment again, the toggle pattern is selected, which appears as expected:

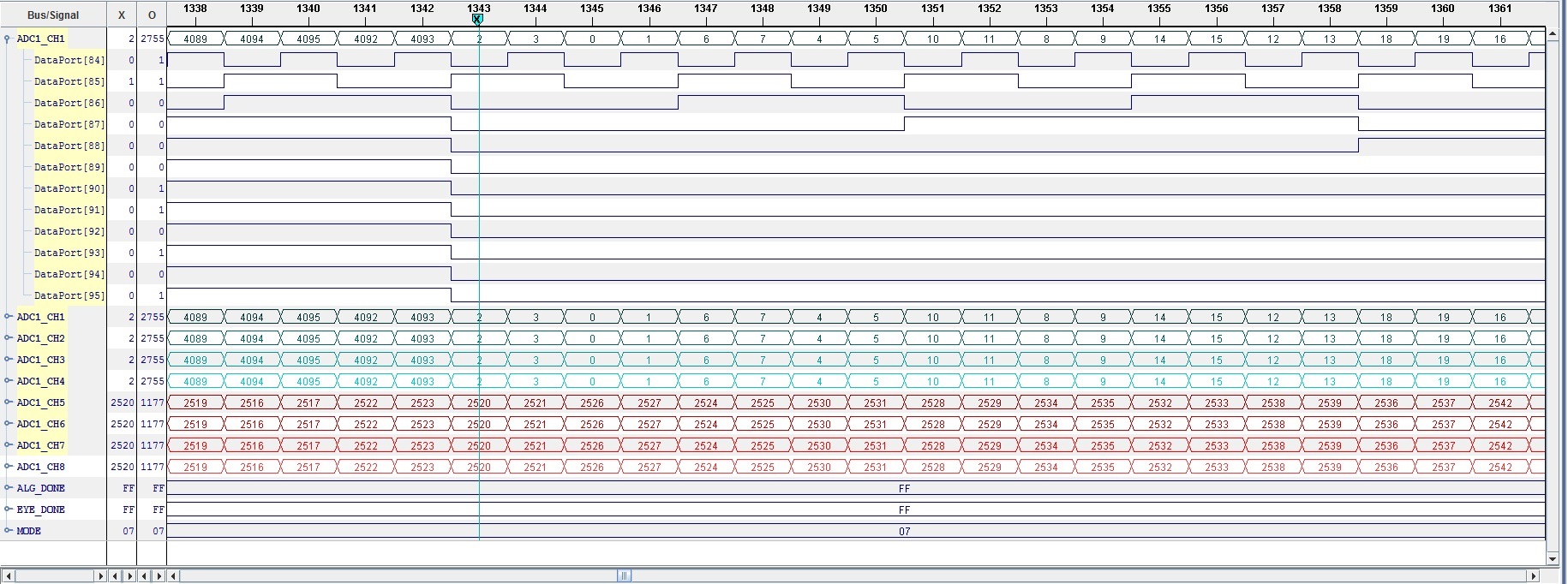

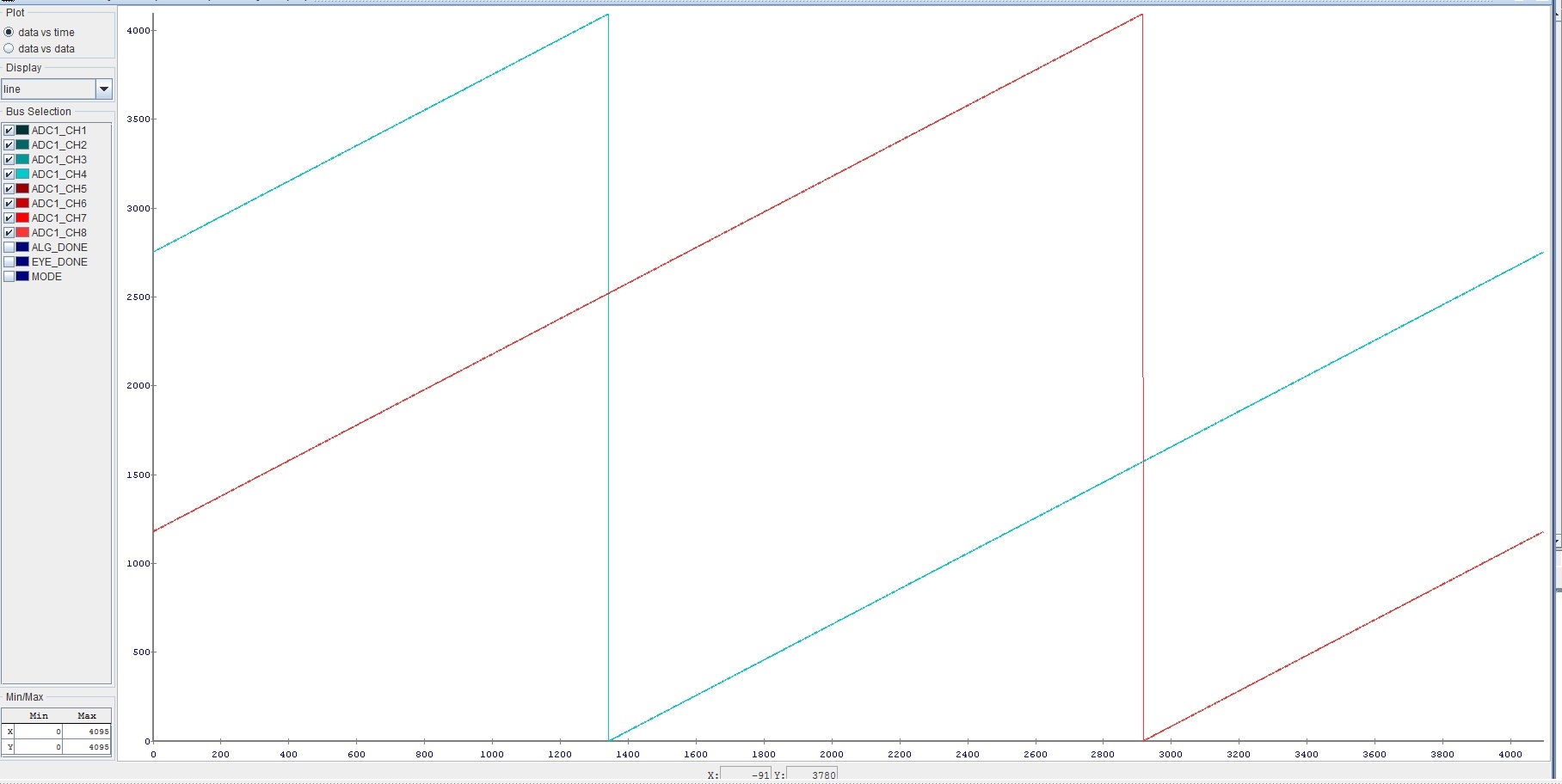

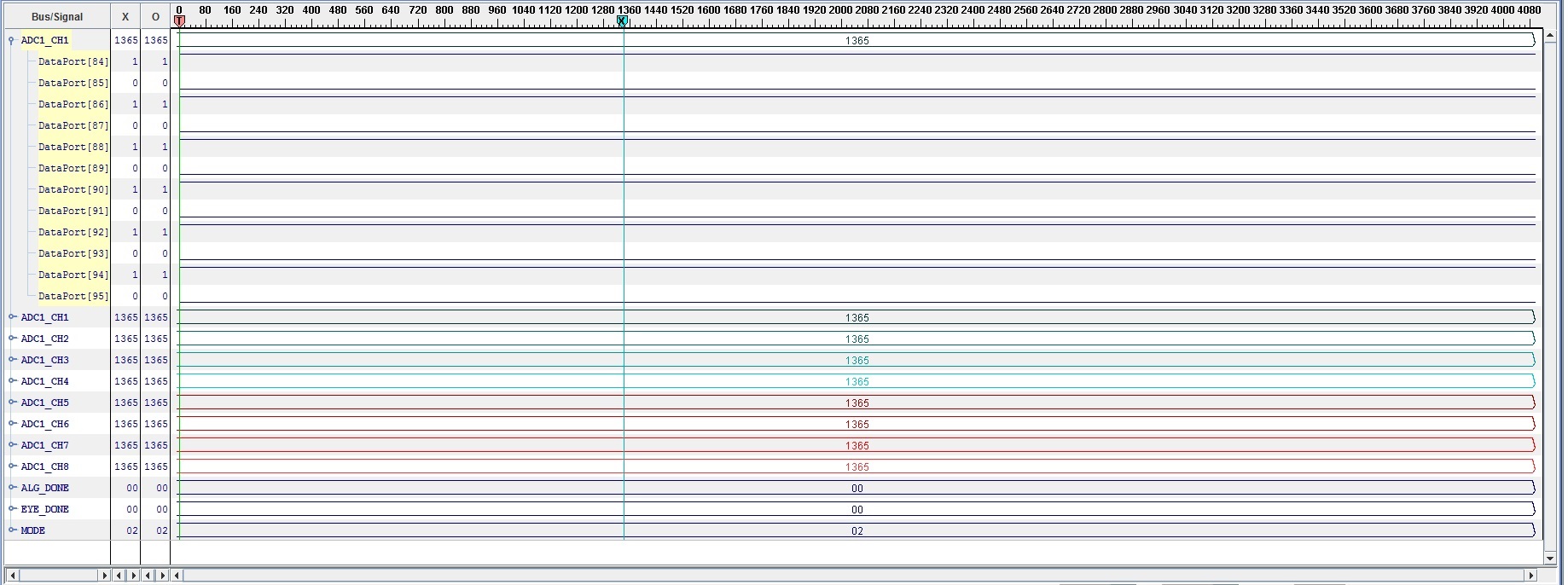

After all, the ramp pattern is activated. At first glance a ramp is visible, but there are two problems I'm dealing with:

Firstly, the deserialized bit "Dataport[85]" (it is bit number 1 from adc data ADC1_CH1[11:0] ) is wrong. Either it is inverted or delayed, I don'know.

Secondly, the ramp pattern of all channels are not in phase. Channel 1 to 4 are aligned, and channel 5 to 8 are aligned too, but with different phase.

So my questions are:

1. Is it possible that the incorrect ramp pattern is generted by the AFE5851?

2. Why are the ramp patterns not aligned, is it correct?

3. Do you think I have a general problem in FPGA receiver logic? How can I determine whether the problem comes from the AFE5851 or FPGA logic, as all patterns except the ramp are correctly deserialized.

Best regards,

Philipp