Part Number: ADS5517EVM

Hello,

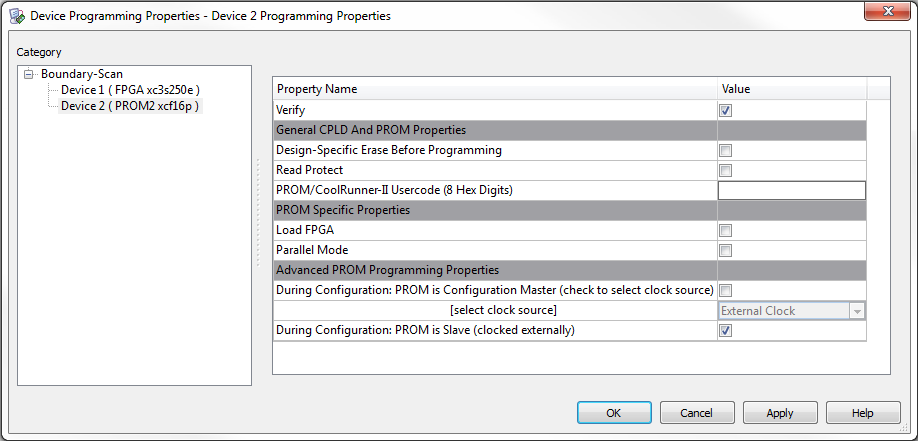

I'm currently using the ADS5517EVM and wish to try modified FPGA code on the onboard Spartan device. I would also like to be able to revert to the original configuration as needed. I believe I would be able to write the custom code to the PROM revision 0 space that is currently inhabited by the ADC CMOS output file and retain the standard LVDS functionality by keeping the original code intact at the end of the PROM, but I would like to avoid this if possible.

Is there any available "original" code for this FPGA?

Thanks!