Other Parts Discussed in Thread: ADS4249, , ADS5463

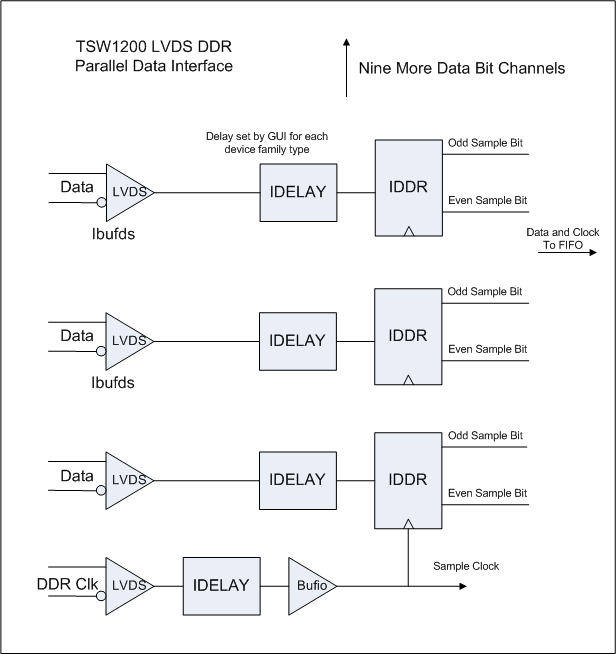

I am working on interfacing ADS4249EVM with xilinx 7series FPGA "VC707". I have received the clock and data from ADS4249 in VC707 according to the block diagram given below but skip the IDELAY portion. the data and clock is received in IBUFDS and IBUFGDS respectively and sent directly to IDDR and then route the output of IDDR (Q1 and Q2) to FPGA IO pins to see the result.

The screen shot taken from an Oscilloscope is given below:

the blue signal in the above figure is the input differential clock from ADS4249EVM to IO pins of FPGA, the orange signal is the input double data rate signal from ADS4249 to IO pins of FPGA and the green signal is the output SDR signal from the IDDR which is routed to FPGA IO pins. The SDR data has both High and Low state at same time, which I am not getting.

Or it is necessary to use the IDELAY even slow sample rate i.e 10MHz

Thanks in anticipation.

Regards