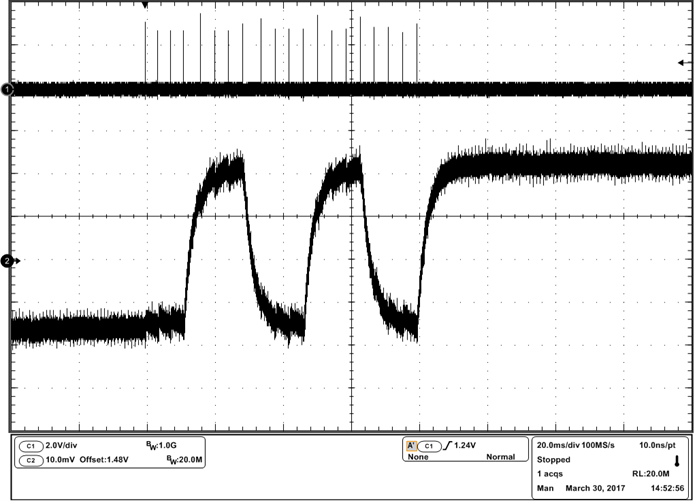

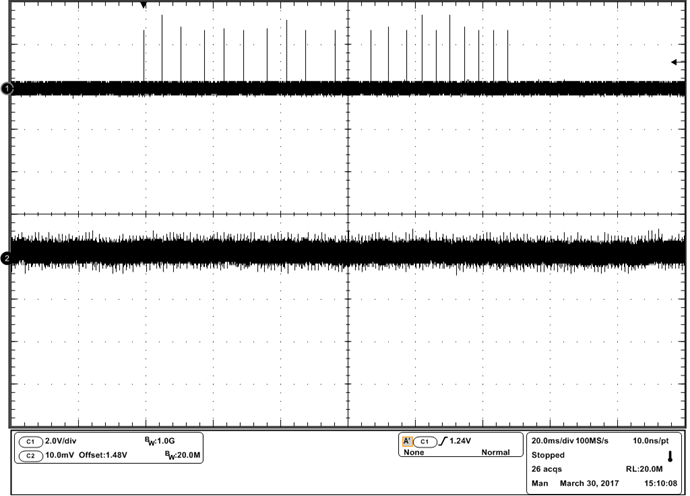

Customer problem for ADC10065 VCOM, VREFT, and VREFB, waveform is attached below.

Please let me know about three points below.

①Are these oscillation normal operation?

Is this oscillation happen normally?

②Please let me know about the theory of oscillation.

③On the datasheet, specification for Internal reference is no described.

Is there spec information for internal reference?

【Additional information】

I think that the one of cause is customer's passive probe.

But previously, I want to know ADC10065's trend of operation.

Best regards,

Satoshi