Other Parts Discussed in Thread: TIPD119, TIPD153

Hi team,

Please let me ask you two questions about DAC7760.

Q1)If HART interface is not used,can the HART-IN pin be left floating?

*In the TIPD119, 22nF capacitor is connected.

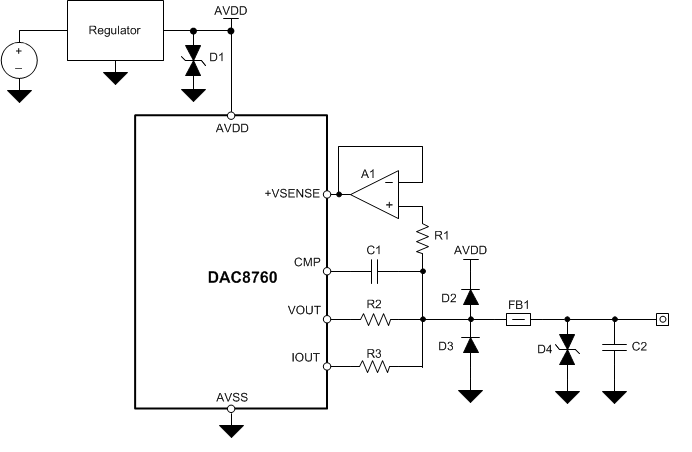

Q2)Could you please tell me the need for a 15 Ω resistor connected

to Vout pin and +VSENSE pin in Figure 96 on the data sheet page 47?

*My customer intends to use DAC7760 in a configuration combined

voltage and current output terminal like TIPD119.

Best regards.

Tsuyoshi Tokumoto