Hi

According to the datasheet, ADS7841-Q1 seems to have clump diode to VCC at input channel (CH0-CH3) because its Vin (analog in) is restricted by VCC+0.3V as absolute maximum ratings.

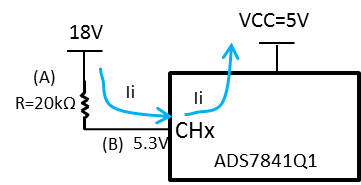

So, the analog Vin(max) must be limited by 5.3V if VCC=5V.

In the customer’s system, we have to consider a situation that 18V may be applied to the analog input channel.

(It is for just in case that it might be happen accidentally, not in normal operation.)

Along with that, we want to offer the way to avoid device damage.

Please see the following image.

(B) If clump diode is present between input and VCC, we think the voltage at CHx would be 5.3V. It is not over absolute maximum ratings.

Then we have questions.

1.

Is our understanding (image diagram) correct?

2.

If our understanding is correct, we think we have to limit input current not to damage ADS7841-Q1.

How much input current can be accepted by ADS7841-Q1 without any damage?

BestRegards