Other Parts Discussed in Thread: LMX2531

Hello,

We would like to have some information on TI ADC P/N ADC08D1020.

We are interfacing the IGLOO2 FPGA P/N M2GL150-1FC1152 with the ADC08D1020 and a probable incompatibility has been observed.

In particular the LVDS clock signal needed by the ADC will be provided by the FPGA with a frequency set at 240MHz.

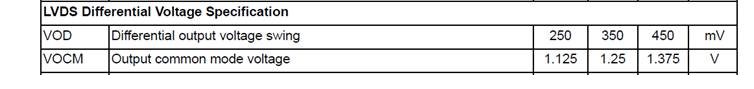

The FPGA generates the clock signal in LVDS standard and in the next picture the Vod parameter is indicated, as reported in the related data sheet.

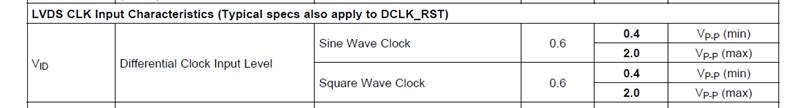

The ADC has the following LVDS CLK input characteristic, as reported in the related data sheet.

It should be noted that the FPGA lowest output LVDS level (Vod) is 250mV, instead the ADC can manage 400mV as the lowest input LVDS signal (Vid).

We would have expected that Vod (lowest) > Vid (lowest).

Therefore apparently the two devices seem to be incompatible even thought the ADC LVDS CLK input is defined, in the related data sheet, as LVDS standard which is the same standard used by the FPGA.

Do you think it could be a real incompatibility or not? Maybe our understanding of the data sheet might be not correct.

If the answer is yes, can you suggest a way to work out with this issue?

Regards

Antonio L.