Tool/software: Code Composer Studio

Hello I have my own design with ADS1291

I have noise problem and cant get a clear signal.

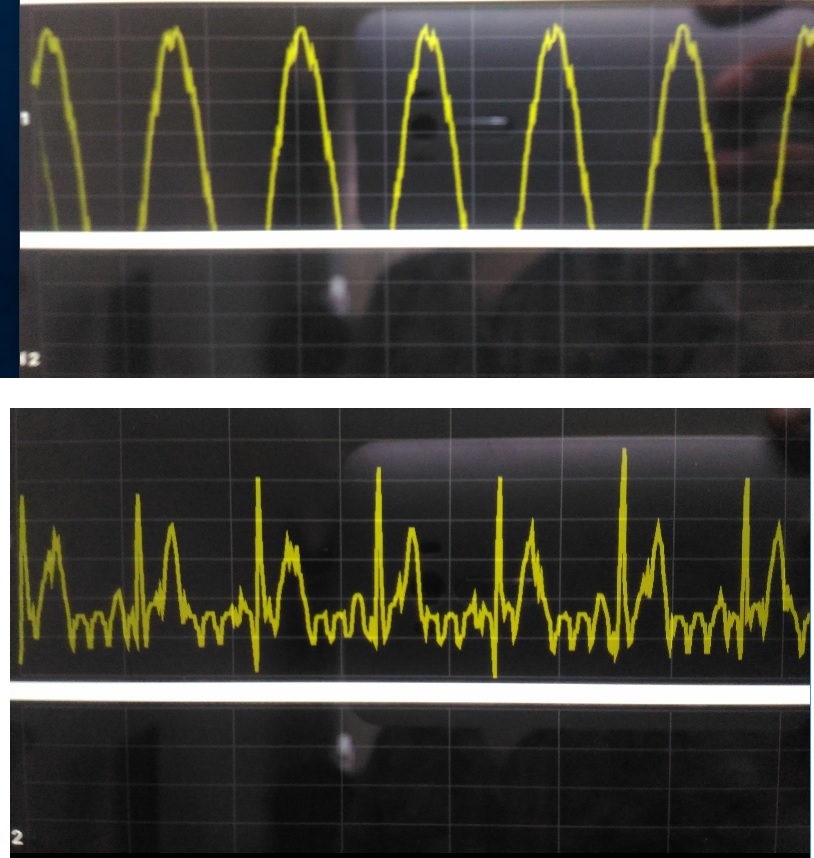

Its being very bad with 500 sps, below pictures with 250sps. Gain set to 1.

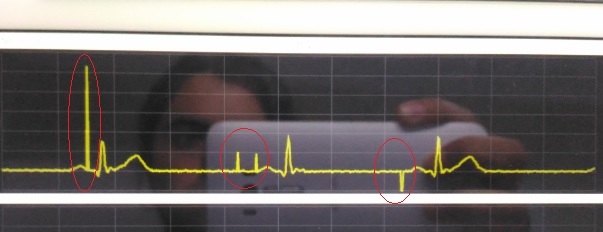

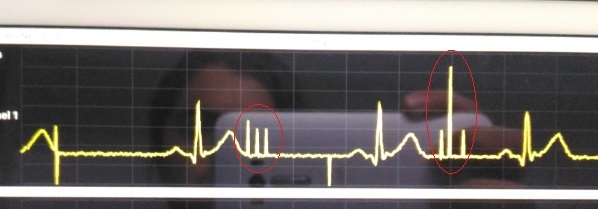

When i touch my hand to patient simulator, its being clear for two pulses than same.

My registers;

0x00, //ID

0x01, //Sample Rate

0xA0,

0x10,

0x00, //CH1

0x81, //CH2

0x00, //RLD SENS

0x00,

0x00, //2.048MHz Select

0x02, //Respiration Off

0x07,

I tried connecting un used RLDINV, RLDREF to VDD.

Regards

Ferhat