Dear Support,

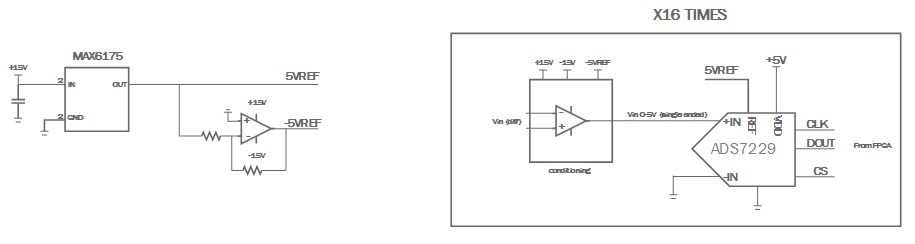

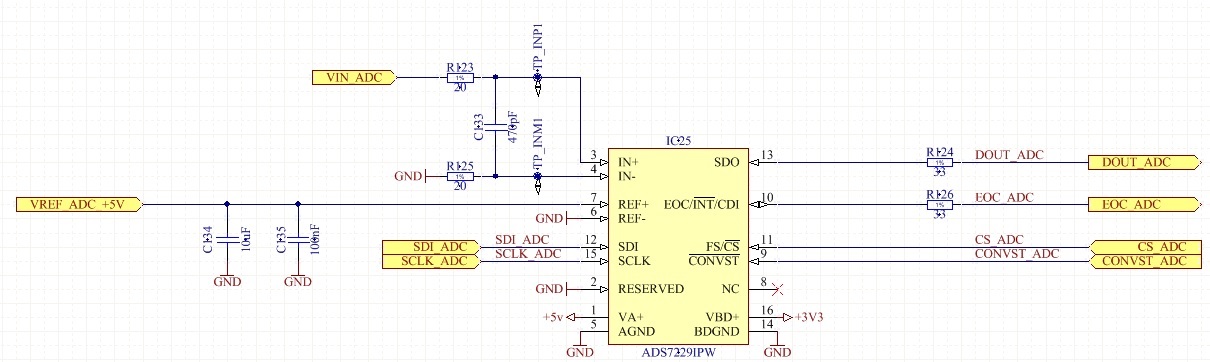

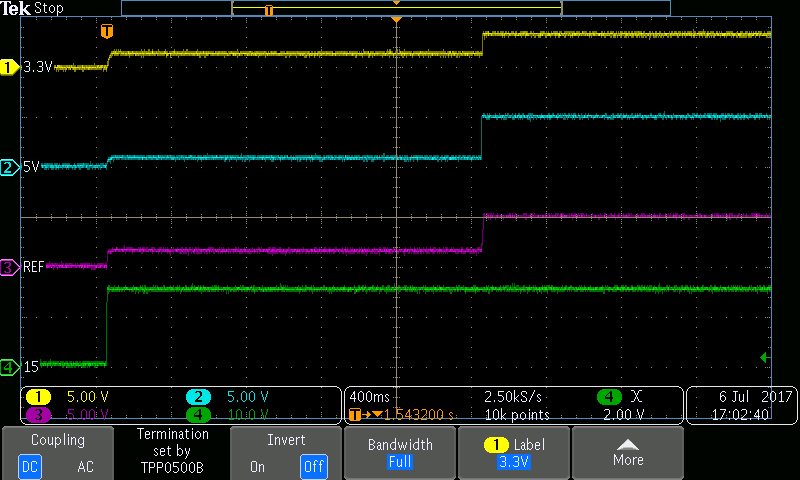

I am writing you concerning a serious issue we are experiencing with the ADC ADS7229. The application I am working on consists of 16 identical acquisition channels based on this ADC. The ADCs are controlled independently by an FPGA and they are referenced by the same +5V reference chip (MAX6175 followed by an OPAMP buffer). Every ADC gets a different conversion start signal issued by the FPGA even though they are synchronous. The board takes as supply: +5V, +/-15V. The +5V supplies the ADCs, while the +/-15V power the conditioning circuits and the reference chip.

The issue is not systematic and it is somehow related to the power-on sequence of the board. It can be described as follows:

-> One or more of the ADCs get “stuck”. What I mean is that when the CONVST goes to ‘0' (conversion start), the EOC remains high and the data line (SDO) is always 0. The issue is not systematic, this means that powering ON/OFF the board the issue might disappear.

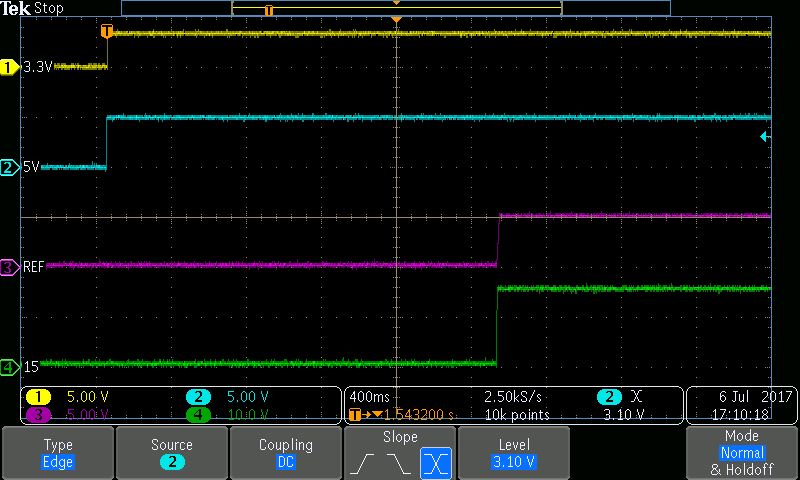

We are using a PXI-based power supply and what we noticed is that this happens when the +5V is activated before the +/-15V. When the +15V is activated before, we do not experience the problem above. Additional information:

- All the ADC state machine timings have been verified.

- The issue is not systematic but when it occurs, it occurs on the same channels

- all the SDI lines of the ADCs are tied together and pulled up to 1 fromt he FPGA

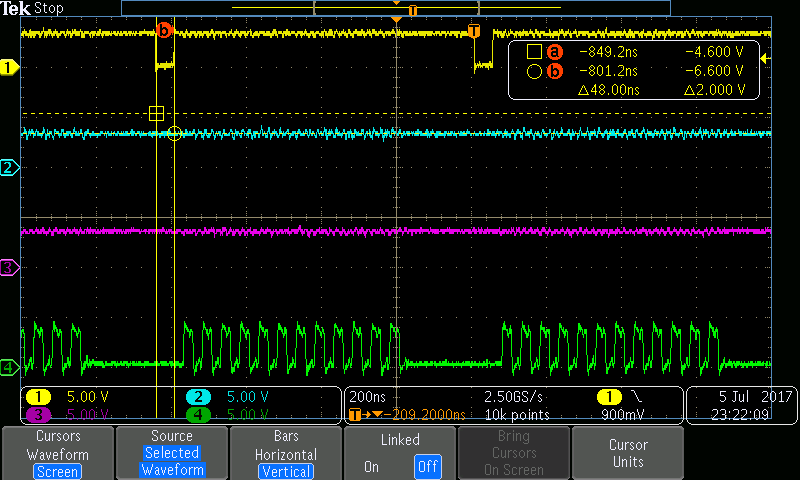

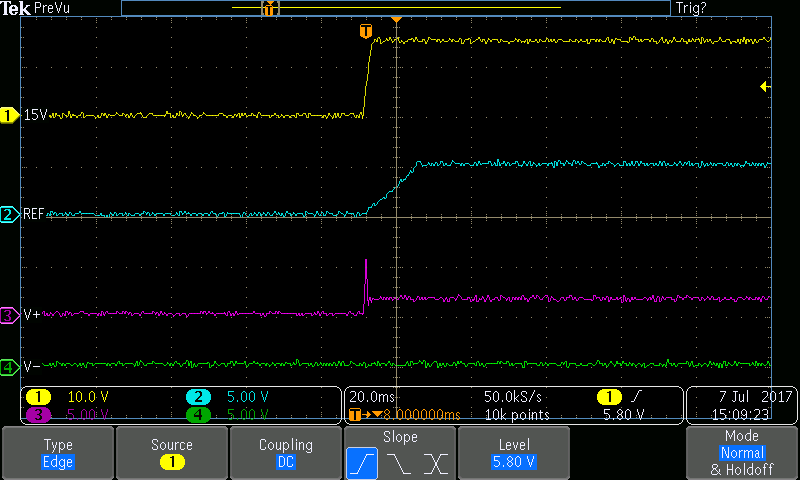

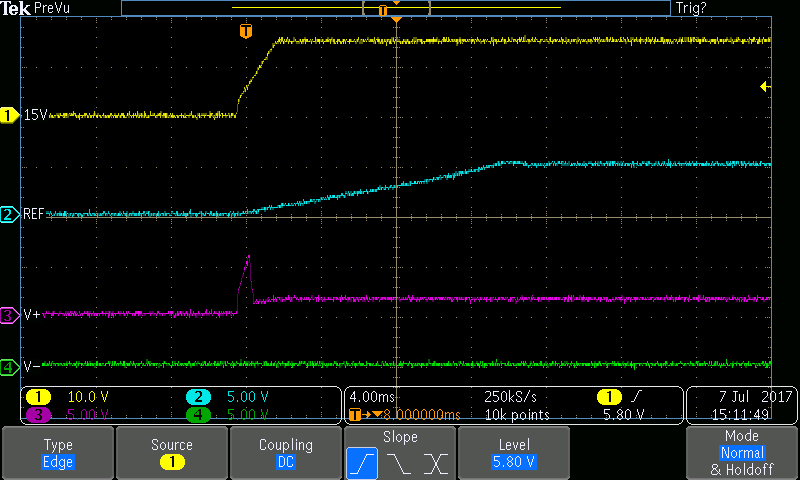

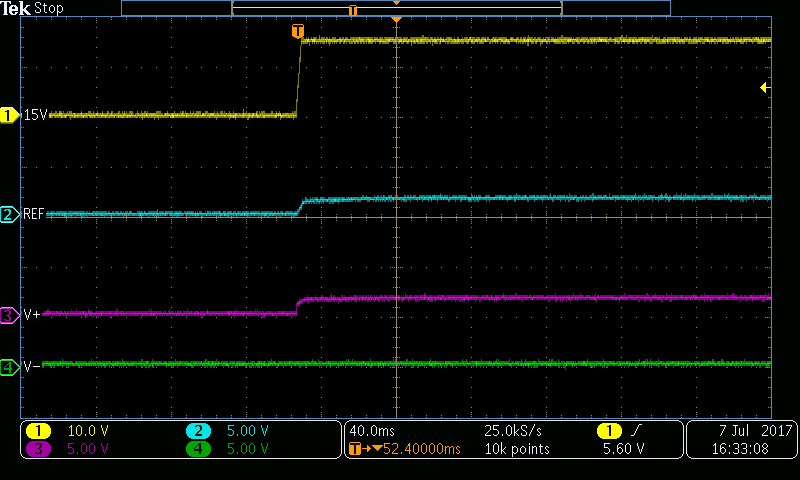

Please find attached two screenshots ( Yellow : CONVST / Blue : DOUT / Purple : EOC / Green : Clock )

1) ADC working properly

2) ADC stuck (CONVST on - EOC not responding)

Diagram

This is a serious problem since we are going into production soon and I am looking forward to receiving you valuable feedback.

Cheers,

Matteo