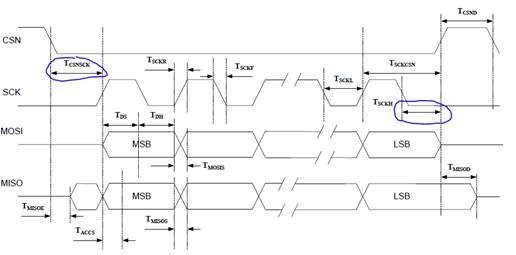

I have implemented the SPI Protocol as described in section 7.3.15.3 of PGA900 data sheet SLDS209A.

Figure 38 "Response to SPI Read Commands is Available When the Next Command is Sent" shows that the first byte of the "Device Response to Read Command" is always 0x05.

Figure 38 does not show what is clocked from the slave during the first byte, "Read Command from Master".

This first byte is usually also 0x05, but is sometimes 0x45.

This response (0x45) seems to appear when the Master and the Slave get out of sync.

For instance, if you perform a SPI transfer to a device on the bus and then change to a diffent device (same bus, different chip select) you get a 0x45 from the PGA900 on the next SPI transfer.

Can someone tell me what this 0x45 actually means?

Was the command actually received correctly received by the salve?

I am using LabVIEW with NI USB-8452, but also tried it with C# and SiLabs CP2130.

Thanks for any help that you can offer.

Ken