Hello HSADC team,

I have 2 questions about Group Delay of ADS1610.

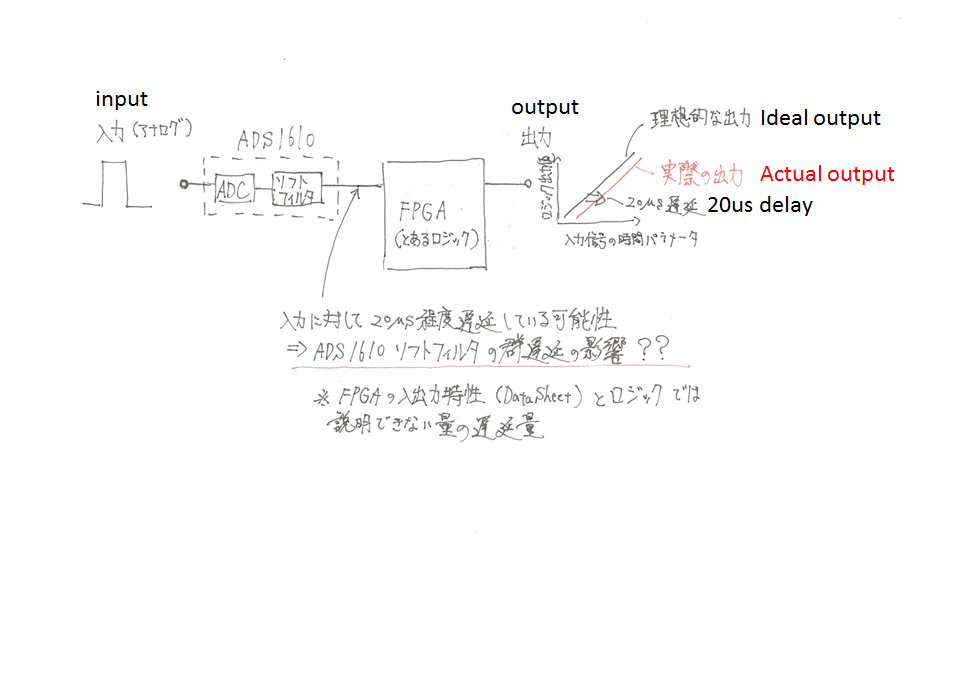

Now customer is using ADS1610 but they facing a problem that ADS1610 seems to have around 20us group delay.

1. As I can see in datasheet page.4, typical value of group delay is 3us@fCLK60MHz.

If fCLK is 50MHz, How much is the Group delay?

2. As I can see in datasheet page.19, reccomended RBIAS resistor values for Different fCLK are like below.

If actual fCLK and RBIAS are different from this reccomentation list, Can this effect the Group delay value?

Thanks,

Yuta Kurimoto