Other Parts Discussed in Thread: ADS1299, ADS1299EEGFE-PDK,

Hello,

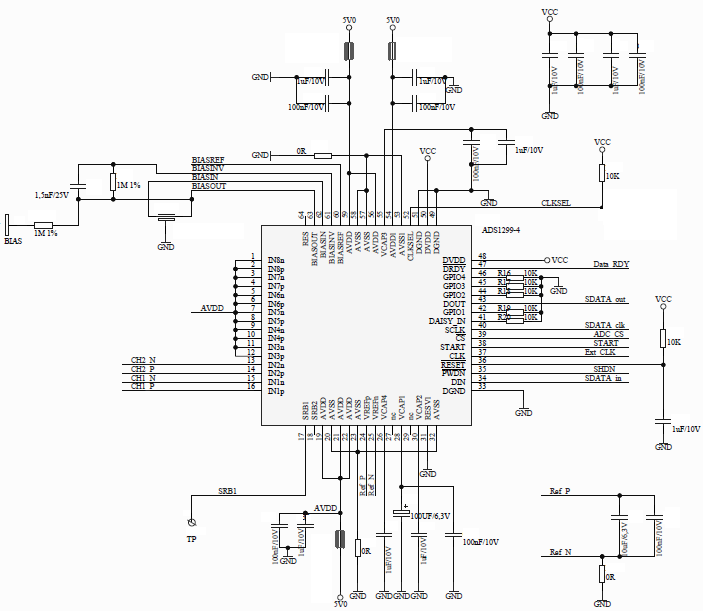

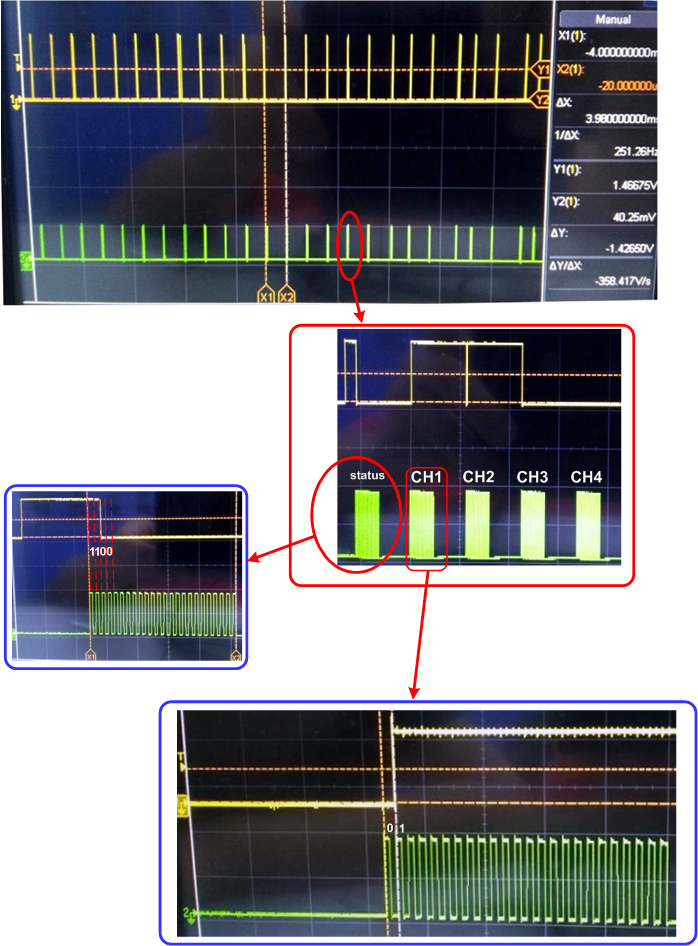

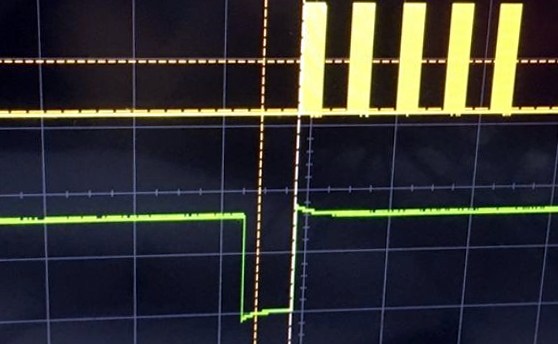

I am working on a custom board using ADS1299-4 , communication with the IC seems fine - ID number reads fine, control registers can be written and read, parameters such a continuous mode and sampling frequency seem to be set without problem. I am now at the stage to get data from ADS1299 but I am facing the issue of not being able to get valid data.

For example, for an uni-polar analog power supply of 5V, when using ADS1299EEGFE-PDK to read the mid-supply value through channel 1 I am getting ADC code of 0x00470F4D and voltage of 2,498142V which both seem correct. With my custom board, however, values I am getting are quite random and do not seem valid - while I am expecting to get ADC code of about 0x00470F4D what I am getting is a sequence of numbers quite random and different from each other, such as

h1 data: 007FFFF0; ch2 data: 00456920

ch1 data: FFFF444A; ch2 data: FFEF0000

ch1 data: FFB3439A; ch2 data: 00020000

ch1 data: FFA345F9; ch2 data: FFB50000

ch1 data: 00664454; ch2 data: FF890000

ch1 data: 007FFFAA; ch2 data: 0044EC74

ch1 data: FFA441F2; ch2 data: 00350000

ch1 data: FFE34533; ch2 data: FFE10000

ch1 data: FFA644AA; ch2 data: 00780000

ch1 data: 006444C1; ch2 data: 007D0000

ch1 data: FFB044C1; ch2 data: 007B0000

ch1 data: FFAD4638; ch2 data: FF970000

ch1 data: FFA64460; ch2 data: 00770000

ch1 data: FFE74545; ch2 data: FFCC0000

ch1 data: FFDC4519; ch2 data: 00060000

ch1 data: 000045B9; ch2 data: 00770000

With other kinds of measurements the situation seems similar, the mid-supply measurement seems to be the most suitable to test the measurement mode, however.

I will be grateful if someone give advice how to debug the problem...