Hi,

Let me ask you a question as below about operating mode of ADS54J66.

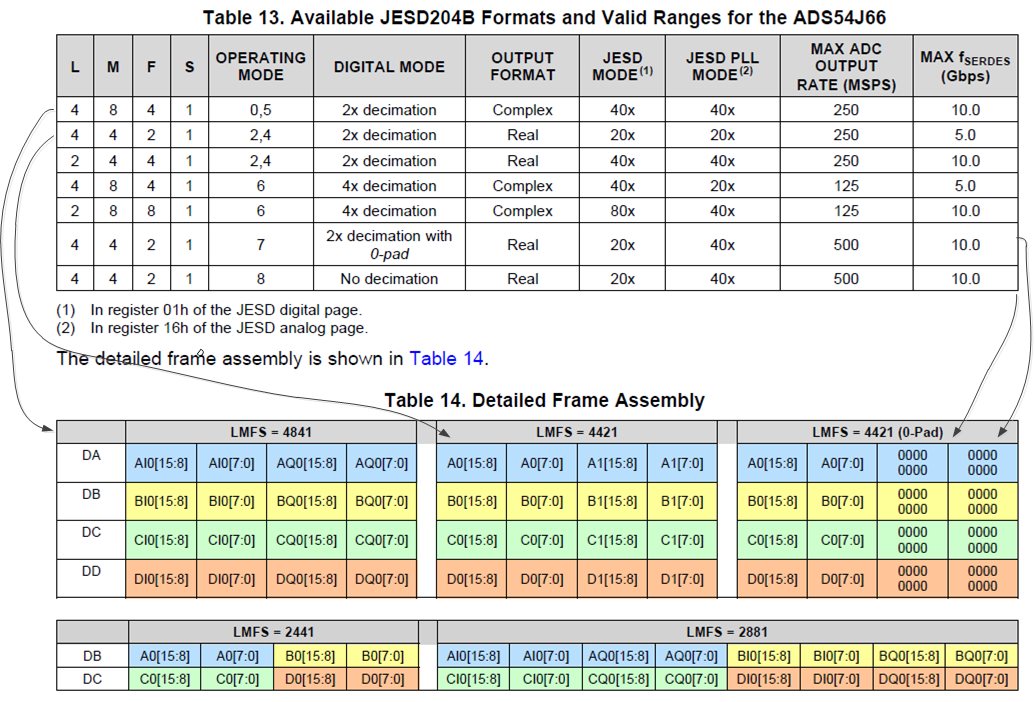

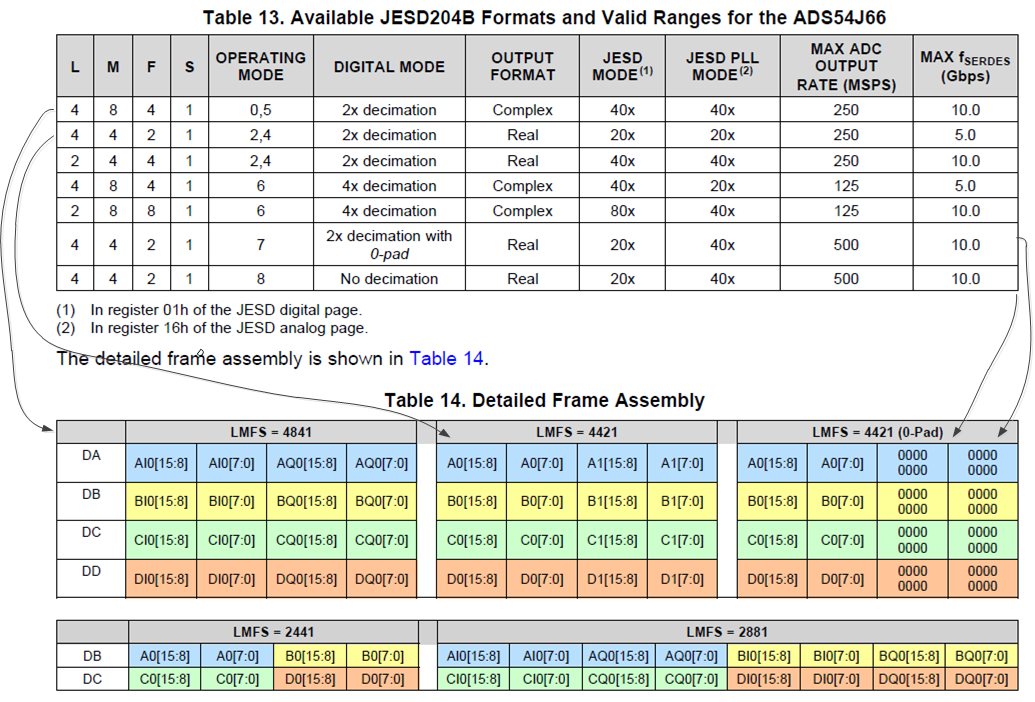

Q1) The data sheet describes below. (datasheet page38, table13 and table 14).

is the line that i connect from the JESD MODE(up) to the frame assembly is the truth(especially the mode 8)?

Q2) in the mode 4421 (not the 4421 0-pad), there is a data named A1.

is A1 the next sample data of A0?

Q3) in the datasheet, (datasheet page38, table 59).

what's the function of the LC register(low resolution counter value) and the HC register(high resolution counter value).

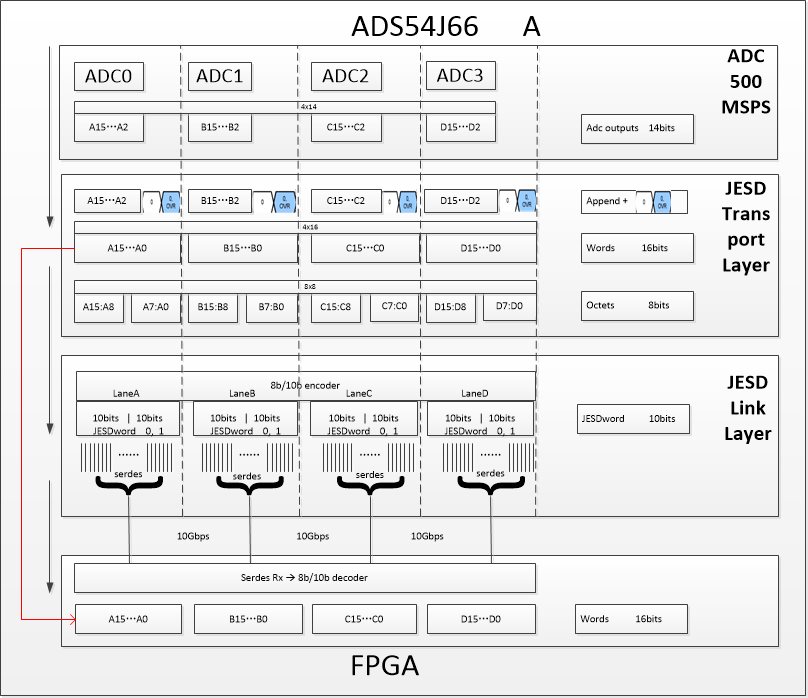

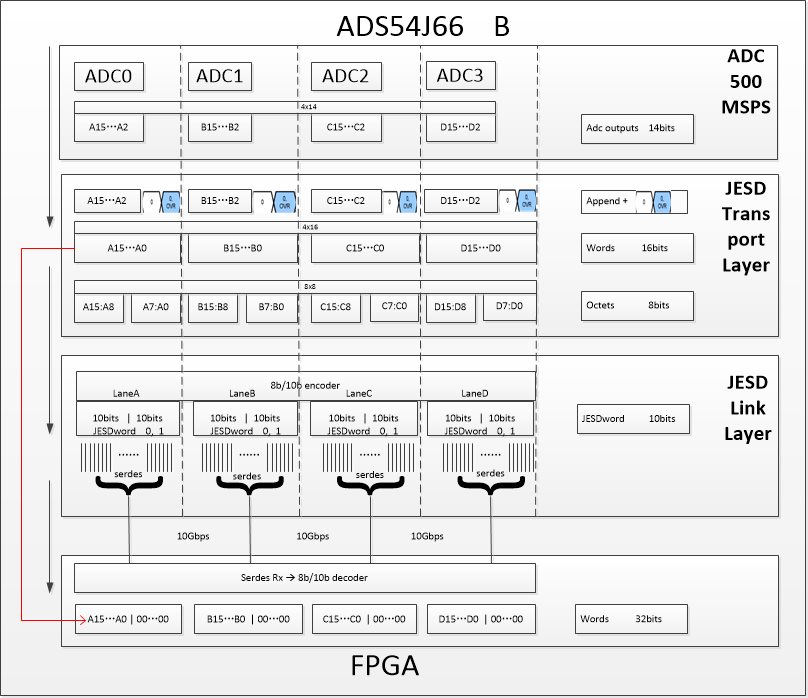

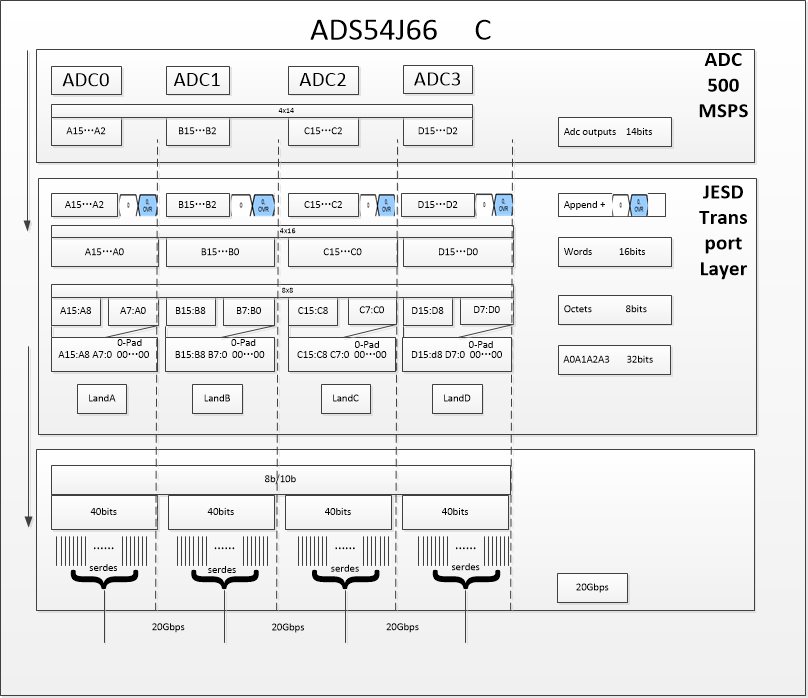

Is it possible to use operating mode "8" (No decimation) in case LMF=244?

I suppose it is possible but let me confirm this to you for sure.

Thank you in advacne.