Other Parts Discussed in Thread: ADC32RF45

Description:

I see a larger than expected frequency-dependent power loss across the bandwidth of the ADC. I’m referring to loss from signal input power at the SMA connector on the EVM board to the ADC output signal. I would like an explanation from TI regarding how much of this loss is attributed to both the PCB and the ADC.

Hardware setup:

- System setup from EVM Quick Startup Guide was followed closely

- ADC32RF45 placed in Bypass LMFS82820 Mode

- ADC Sampling frequency = 2949.12 MHz

- 2nd Nyquist Zone operation

- ADC Fs signal creation: sig-gen à BP Filter à Splitter à LMK Ref & ADC Clock

- Input signal creation: sig-gen à BP Filter à Splitter à Spectrum Analyzer & ADC Input Ch. A

- EVM Configuration Files: “LMK_ ADC32RF45_LMF_82820_ExtClock.cfg” and “ADC32RF4x_12bit_LMFS_82820.cfg”

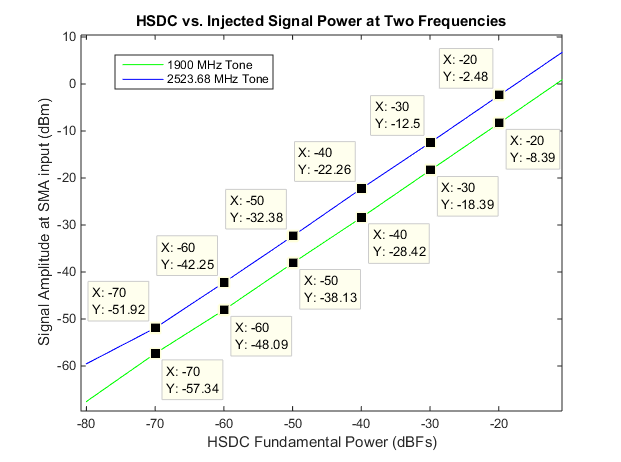

Test 1:

In this test, I selected two frequencies as input signals and swept the input power level. I selected 1900 MHz because it was the recommended frequency in the EVM Quick Startup Guide. The second frequency (2523.68 MHz) was selected because it was the same offset from the center of the band as 1900 MHz. The X-axis shows the power levels as reported by the HSDC software while the Y-axis represents the measured signal input to the EVM board. Over these measurements, a mean of approximately 6 dB in signal level change seen between these two frequencies.

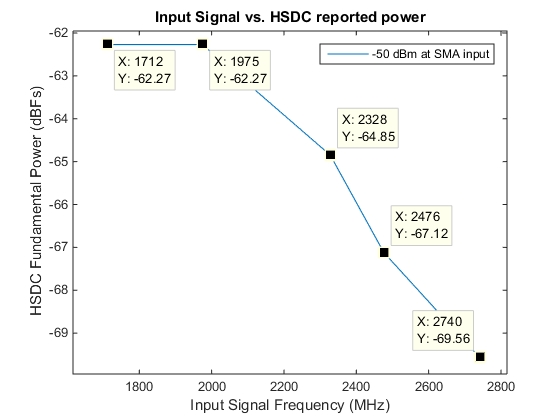

Test 2:

In this test, five frequencies (1712 MHz, 1975 MHz, 2328 MHz, 2476 MHz, and 2740 MHz) were chosen such that the entire instantaneous bandwidth of the ADC was covered while ensuring that none of the main spurs (interleaving or nth order) overlap. The injected signal amplitude into the SMA connector was set to be -50 dBm for each test frequency. The X-axis represents the input signal frequency while the Y-axis shows the fundamental power level reported by HSDC. The plot shows a 7.29 dB roll-off in ADC power over the frequency range tested.