Part Number: ADS5407

Other Parts Discussed in Thread: DS10BR254,

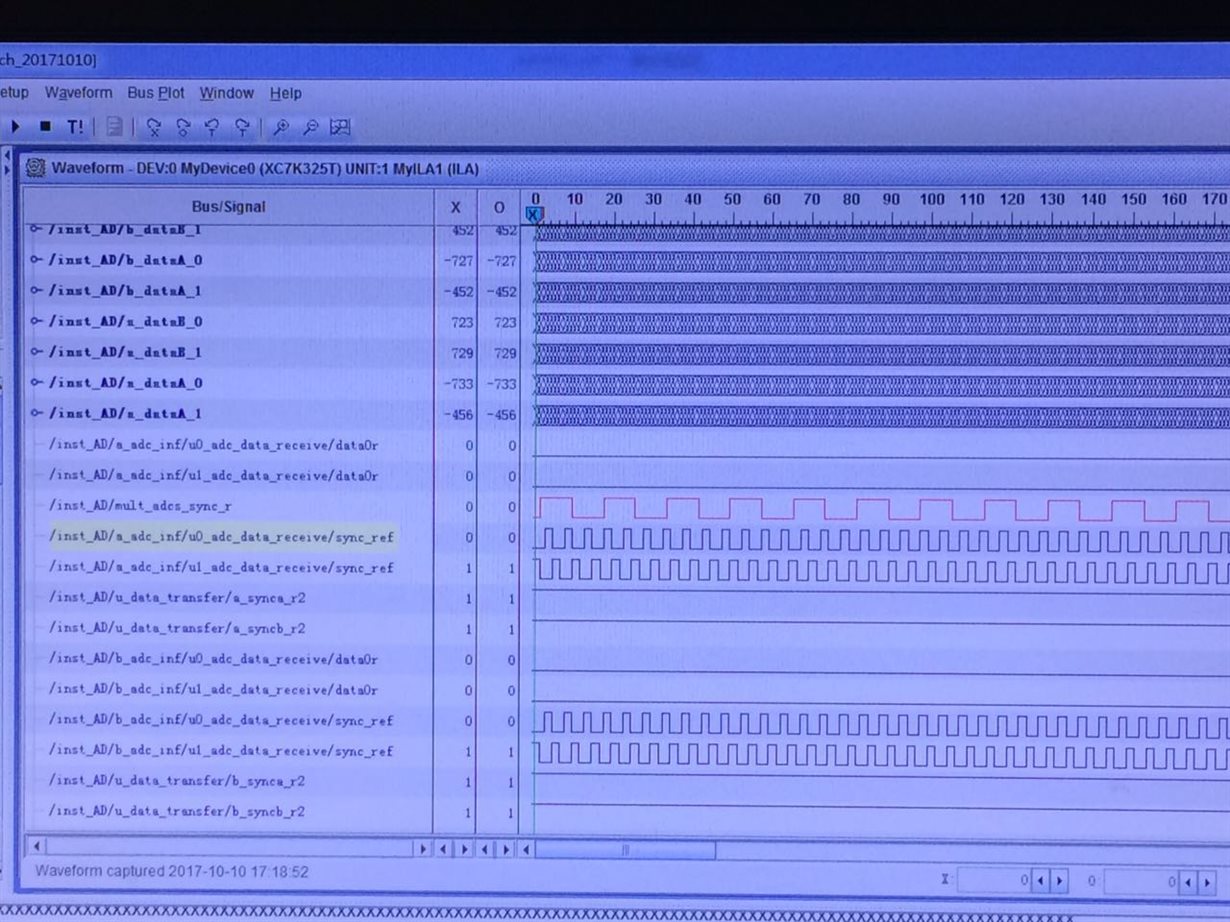

In my project, i have to synchronize 64 ads5407s on 16 platforms with K7(xilinx) fpga, and now i have such problems as follow:

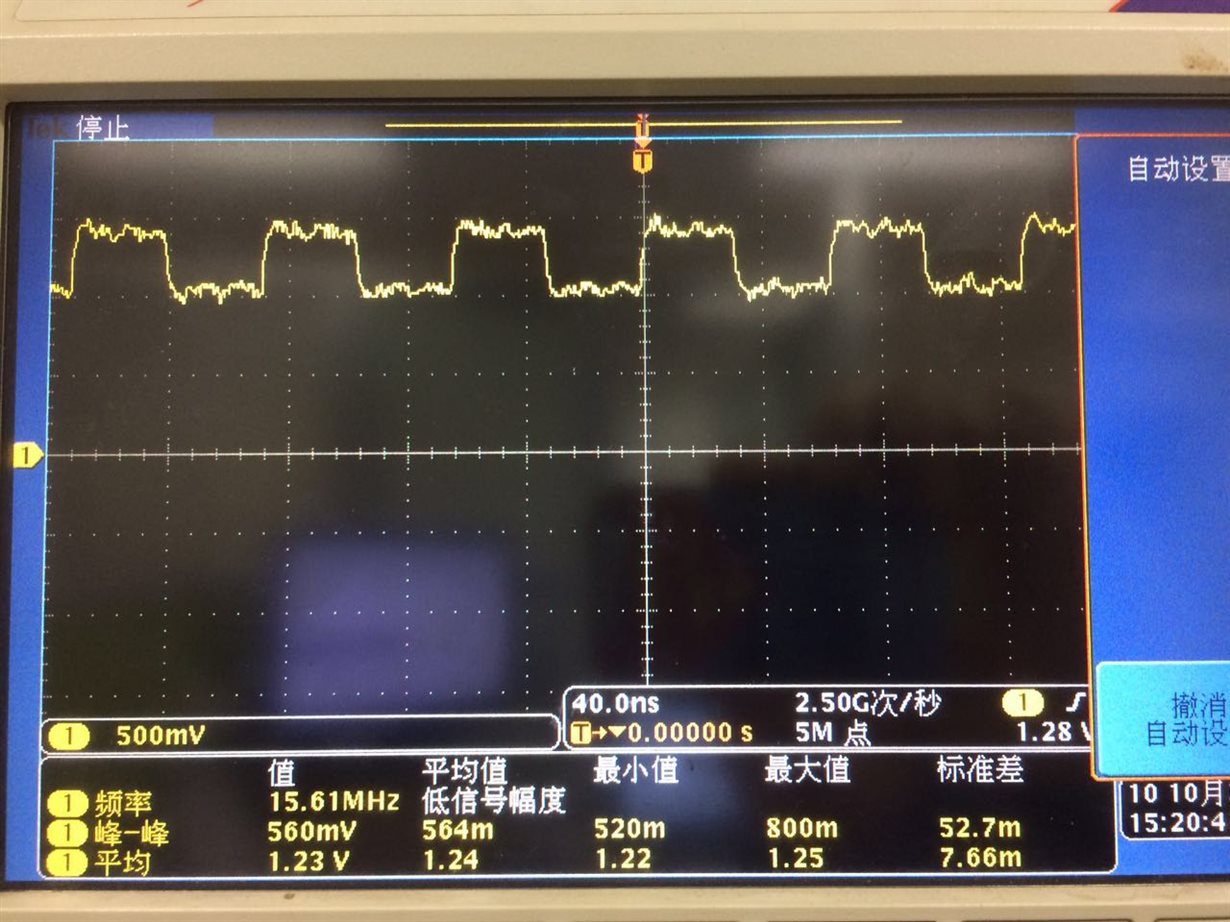

i have SYNC signal through a lvds buffer (DS10BR254) to link to ADS5407 in dc-coupled , but i find that SYNCOUT signal is not a perfect pulse sequence as a signal comes from a 5-bit counter mentioned in ADS5407 datasheet.

i do set HP Mode=1, (0x01, D1)

So, i think the adcs are not synchronized correctly and i suppose whether i operate with some wrong steps?

And you can contact me via email, my email address is zhouleichen@163.com

Thanks,

ZhouLc