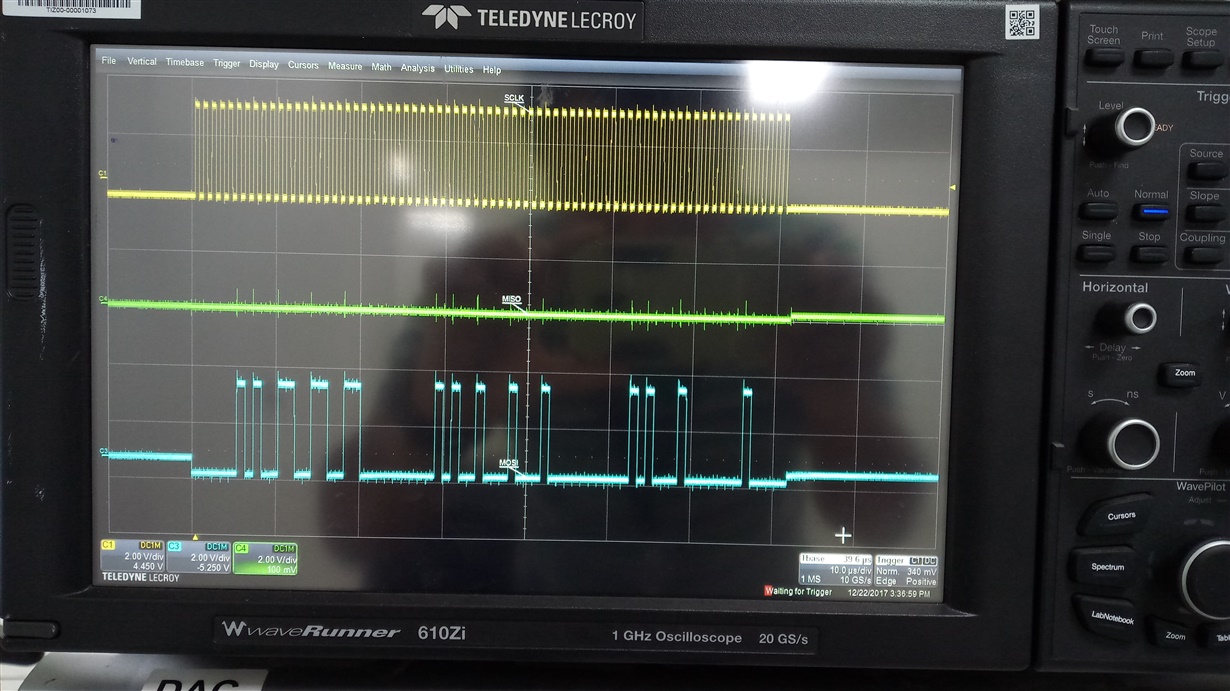

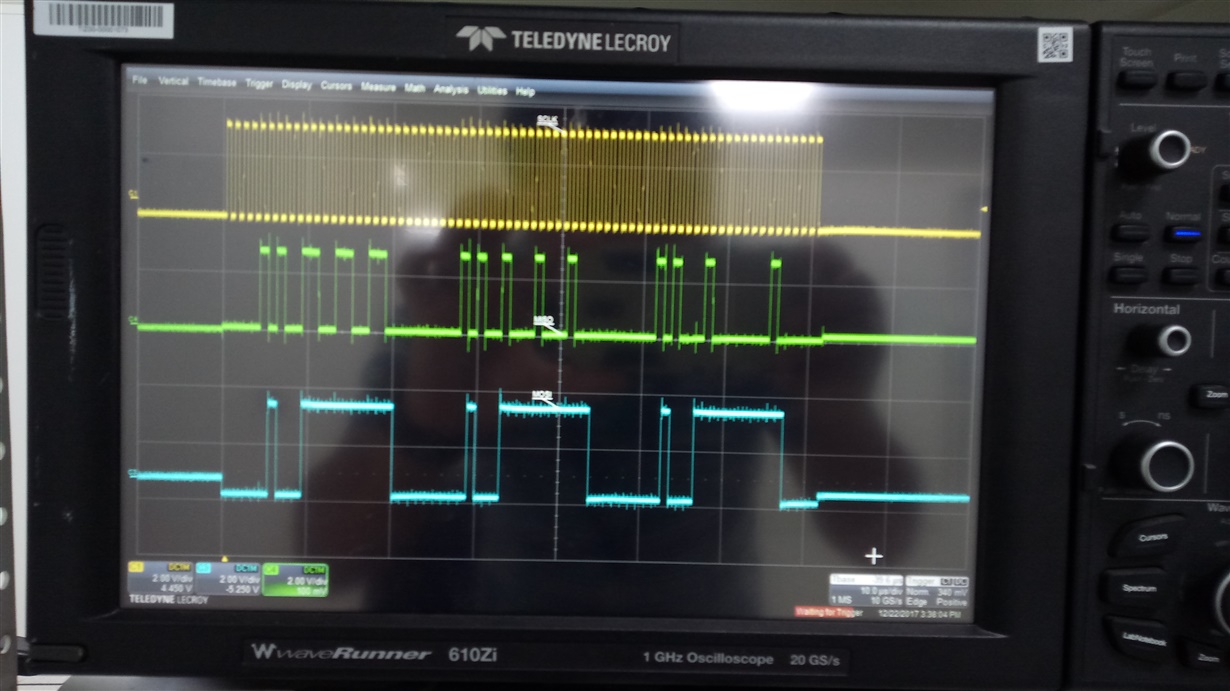

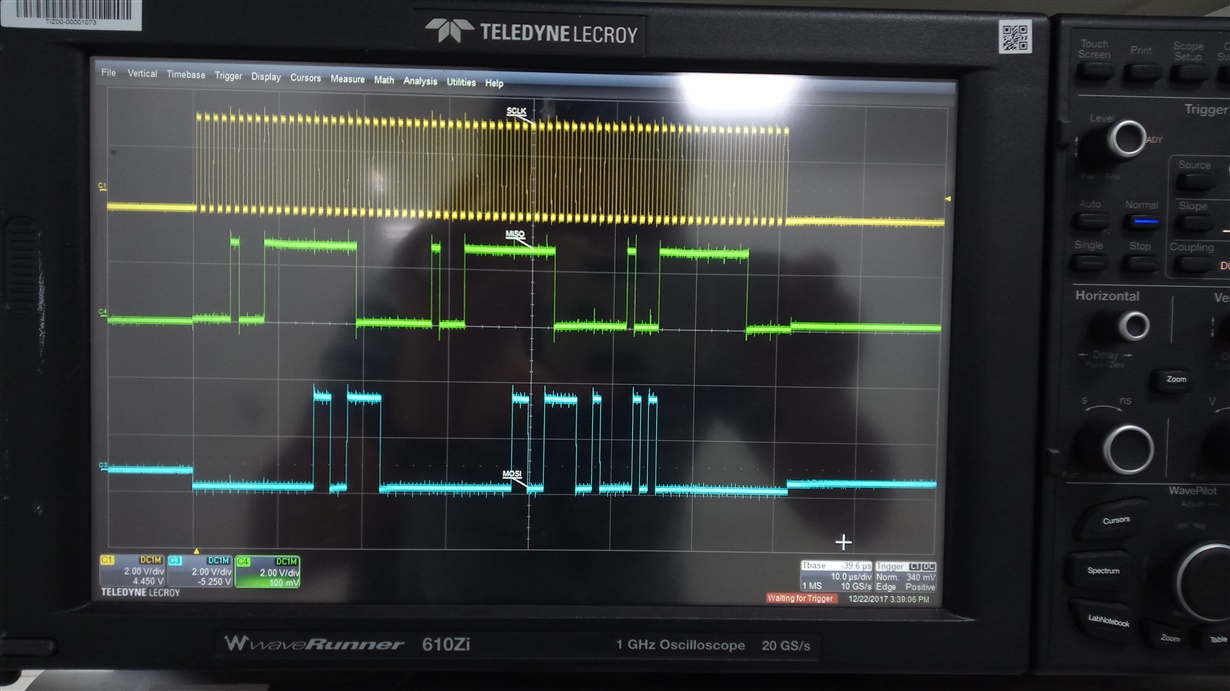

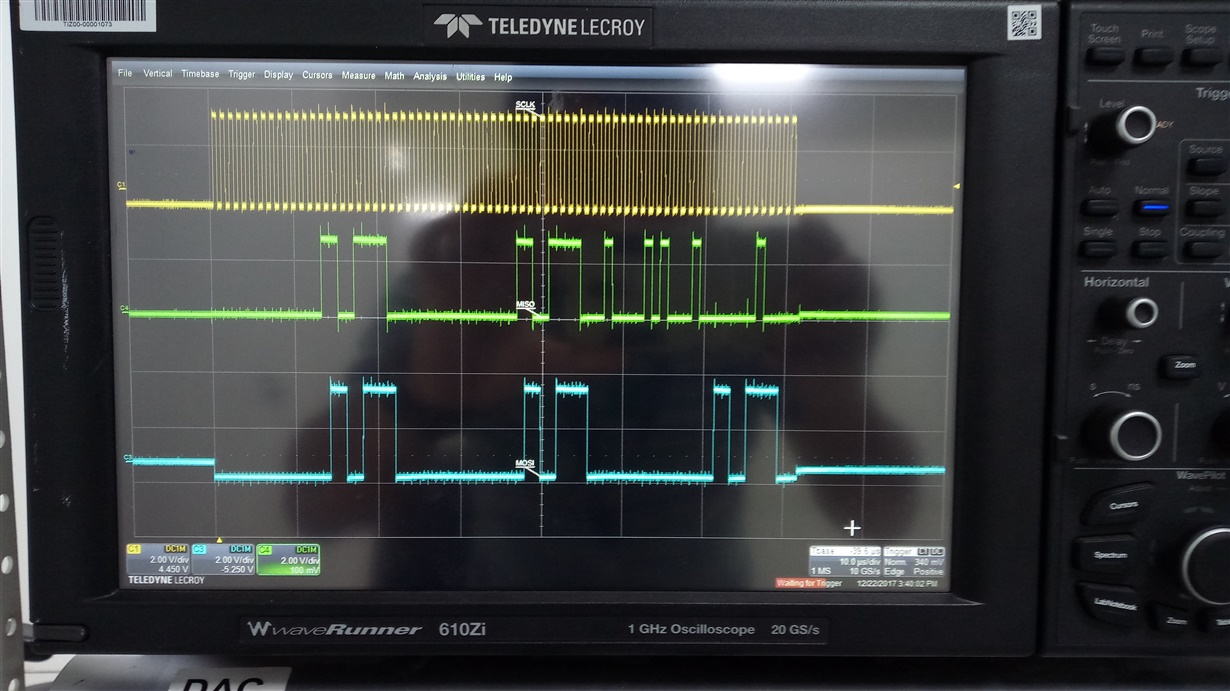

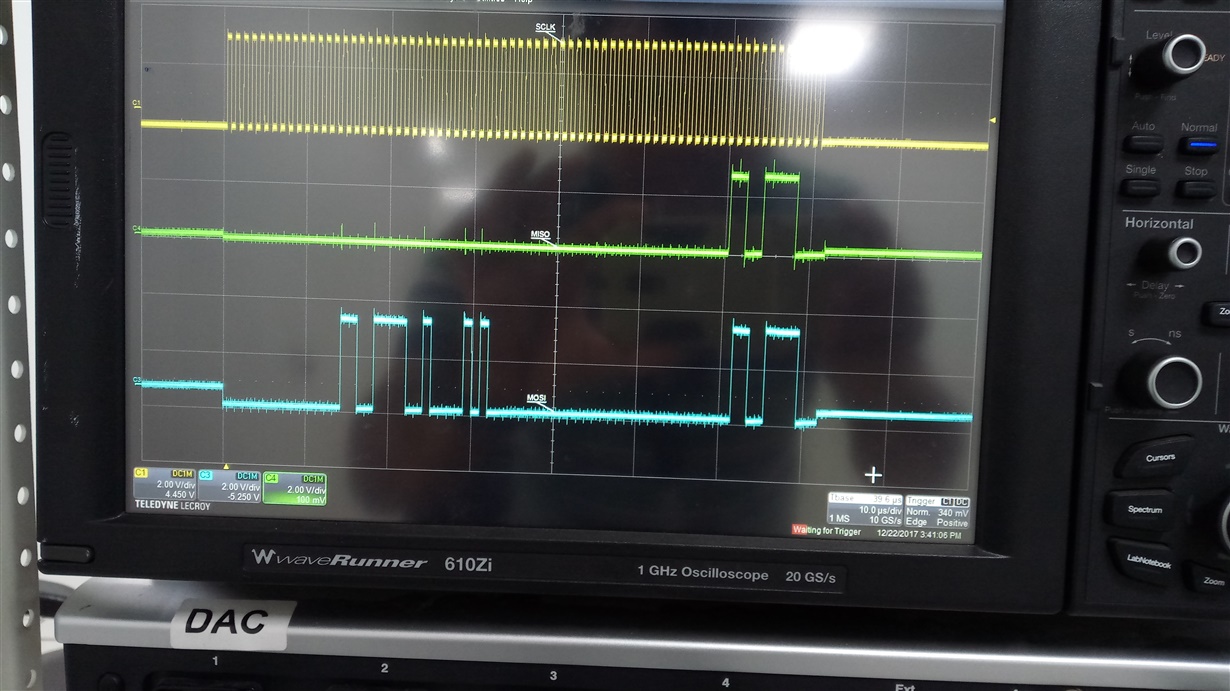

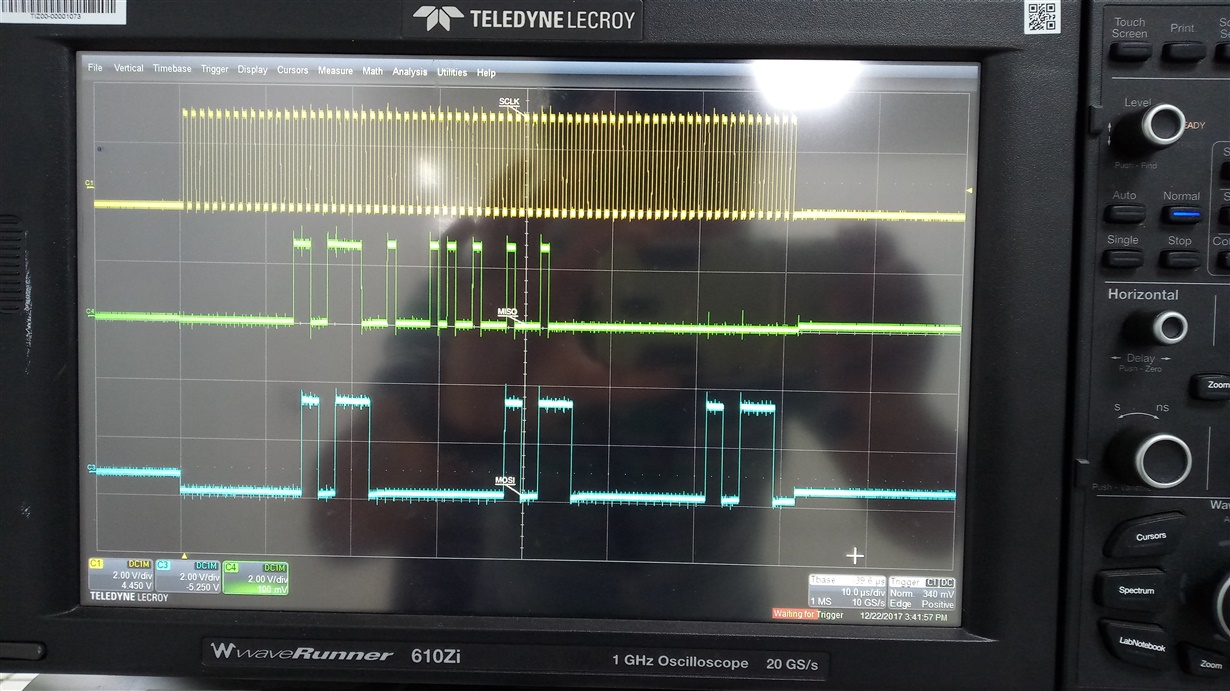

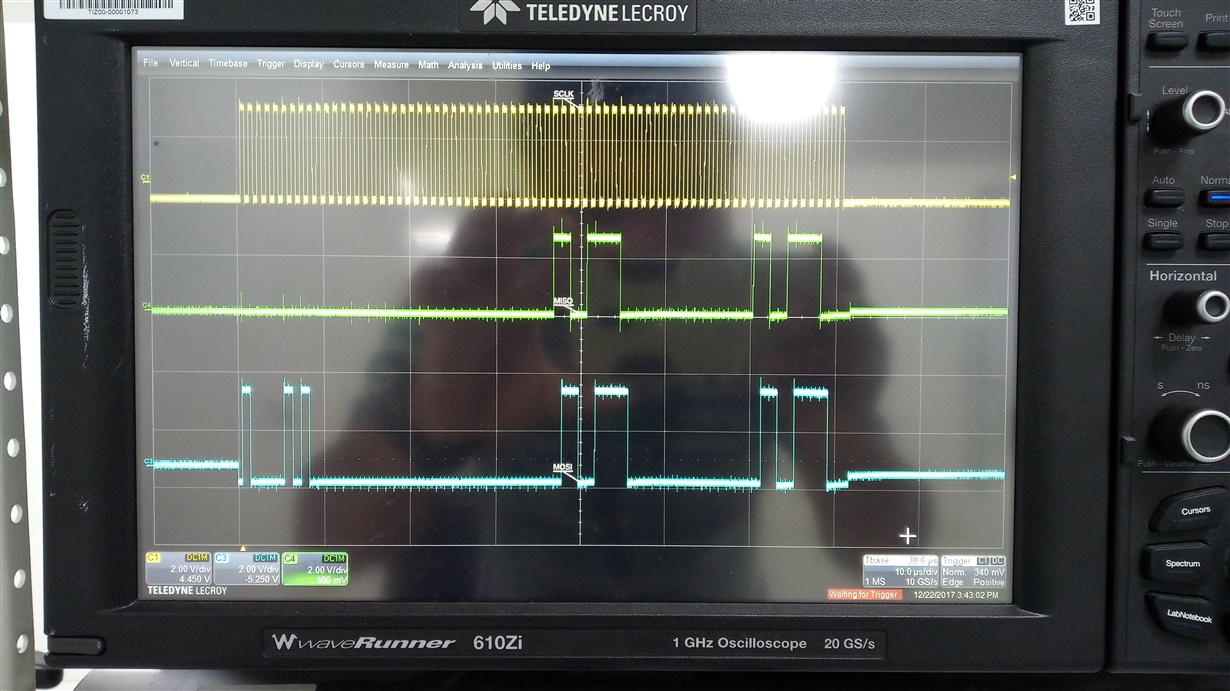

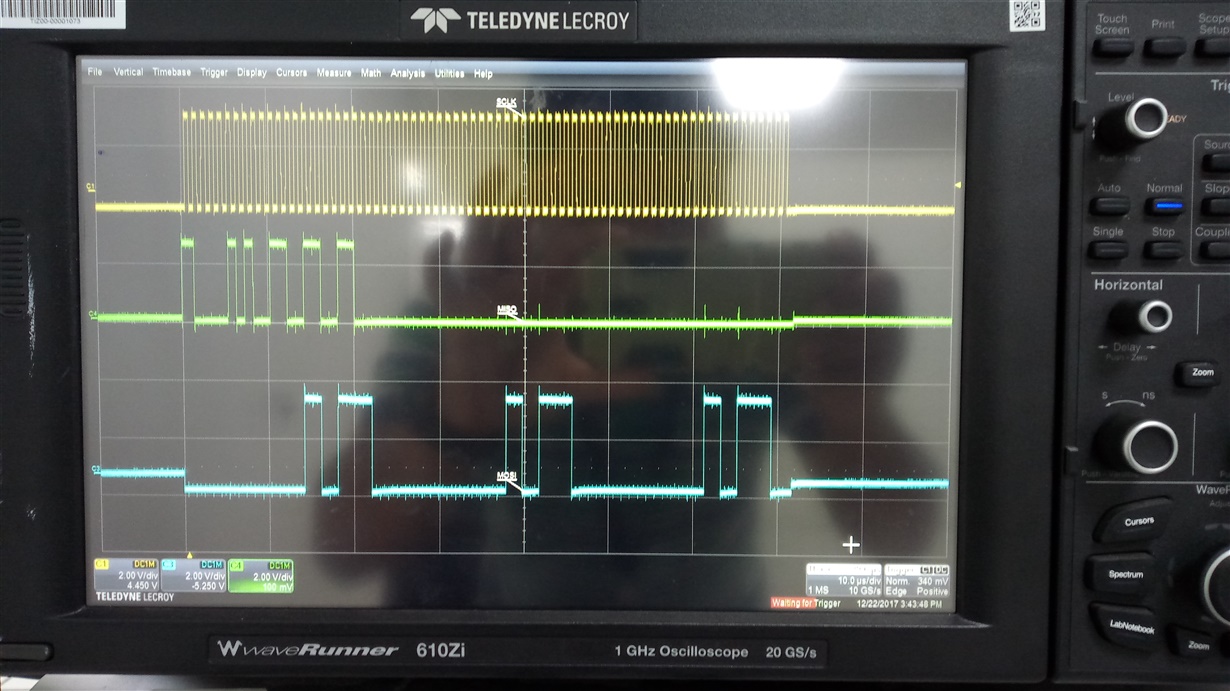

Hello, we're using the DAC7716 in a design where 5 DACs are daisy-chained, i.e. there's a common clock and CSn and successive MOSI/MISO are linked. There is no problem performing daisy-chain mode writings, as indicated in the datasheet Fig. 2. The daisy-chain readback doesn't work however, although all readback timings from Fig. 3 are respected. There is no specific figure for *daisy-chain* readback mode in the datasheet and moreover it is not working as expected (many zeros returned in the 120-bit vector) which makes us wonder if it is indeed supported? Since the data is shifted out when CSn is high I don't see why it wouldn't work (theoretically). Thanks for looking into this.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.