Other Parts Discussed in Thread: ADC12D1620QML-SP,

Hello,

I am using the ADC12D1600QML in a receiver application where:

Sampling rate (Fs) is 1280 MHz;

Input tone (Fin) is 539.9 MHz (~3 dB below full scale)

Demux (2:1) mode is used;

Non-DES mode is used;

Calibration run as indicated in dataheet

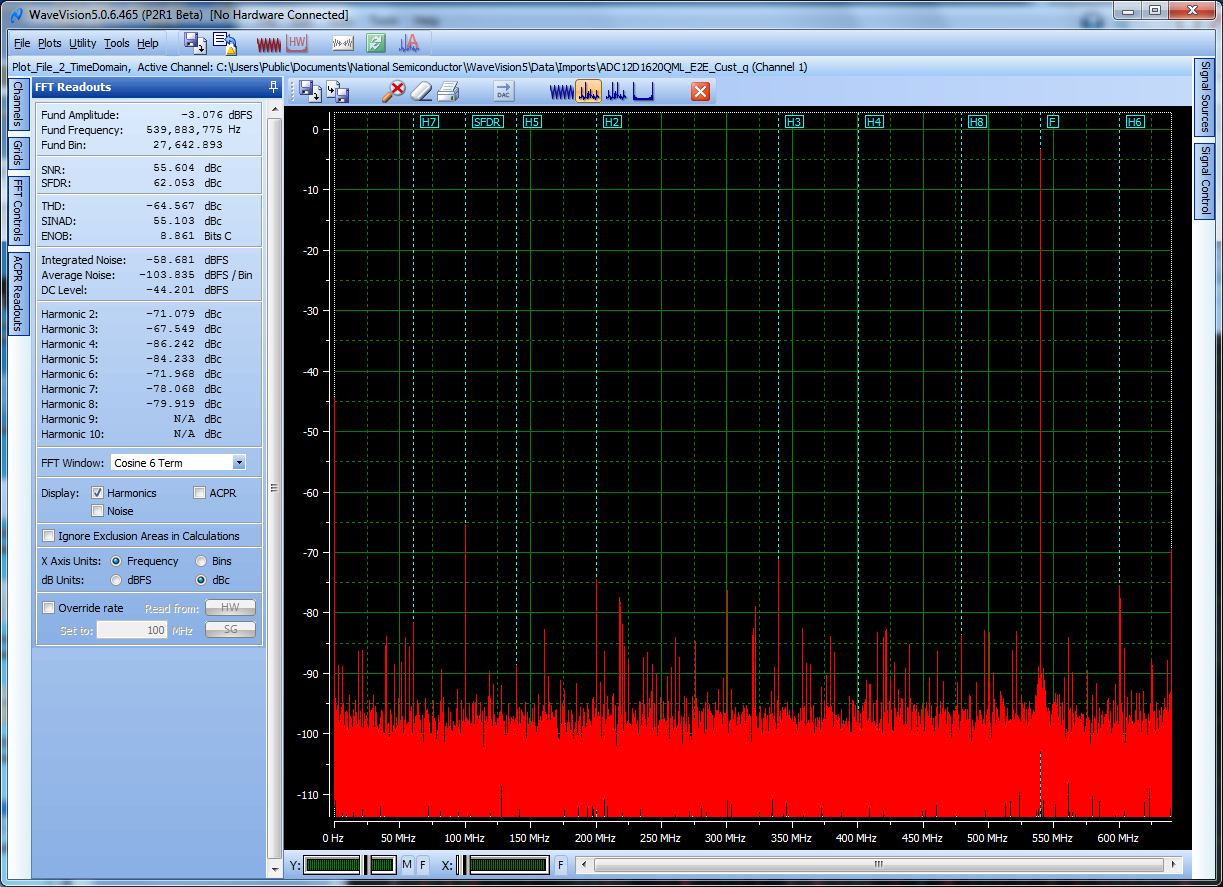

Collected data shows the expected fs/4 spur (320 MHz) due to DCLK coupling. However, we are also observing spurs at Fs/4+Fin and Fs/4-Fin. These spurs seem consistent with quad sub-converter operation (e.g.running in DES mode) but I am unsure why they are appearing in this Non-DES configuration. The input tone is filtered such that all harmonics/spurs are -75 dBc. Below is a "representative" plot of raw FFT data from the I channel.

Any thoughts on why we may be seeing the Fs/4+Fin and Fs/4-Fin in non-DES mode would be appreciated.