Other Parts Discussed in Thread: ADC12J4000, ADC12DJ3200, LMX2581, LMK04828

Hello!

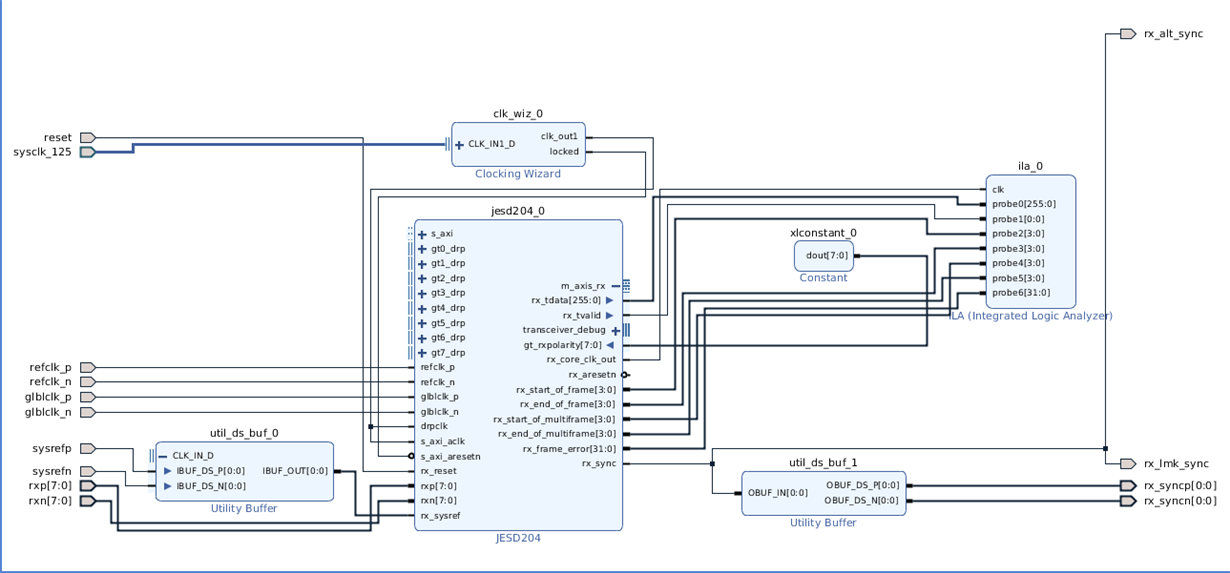

I'v got adc12j4000EVM rev.E3 and I try to connect it to my vcu108 xilinx board. Bypass mode 3760 Msps.

According the datasheet for this ADC I am using following parameters for jesd(xilinx jesd 204b ip core v7.1) - for default parameters from adc gui:

F=8

K=4

L=8

LineRate = 7.52Gbps

ReferenceClock = 188MHz

SYSREF on Positive Edge

Using global clock 1

scrambling on

sysref always on

sysref required on re-sync

In additional transceiver control ports I'v changed polarity for gt_rx ports; In ADC gui v1.1 I press button "program clock" in bypass mode; And for test I am turning on Short/Long transport test.

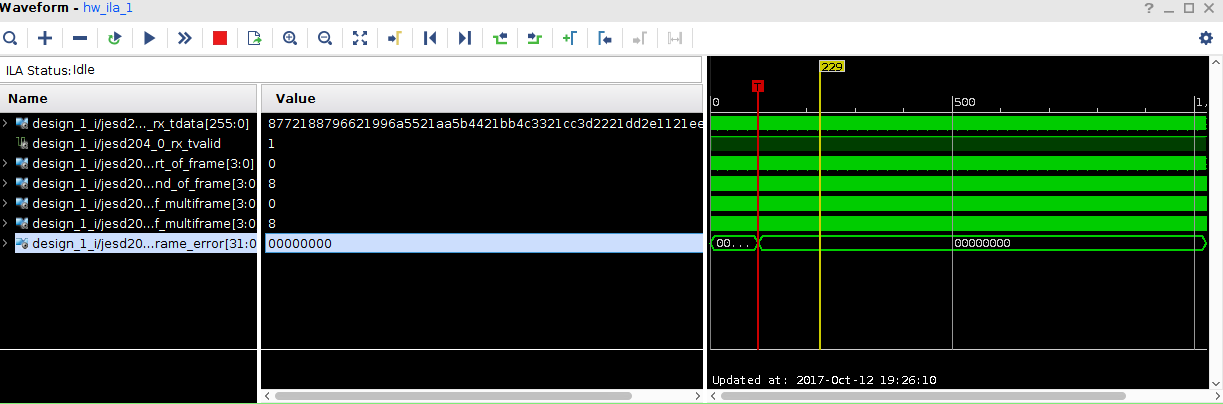

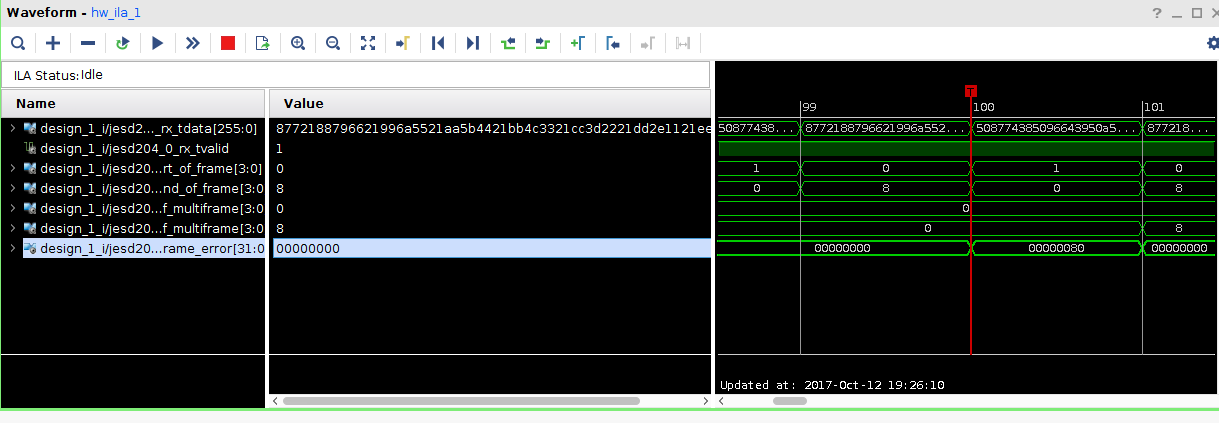

So I expect to see rx_frame_error bus all zeros and the sequence on output bus.

But I have infrequent errors. What may be the reason of such problem.

(block design and chip scope print in attachment)