Other Parts Discussed in Thread: ADS1292R

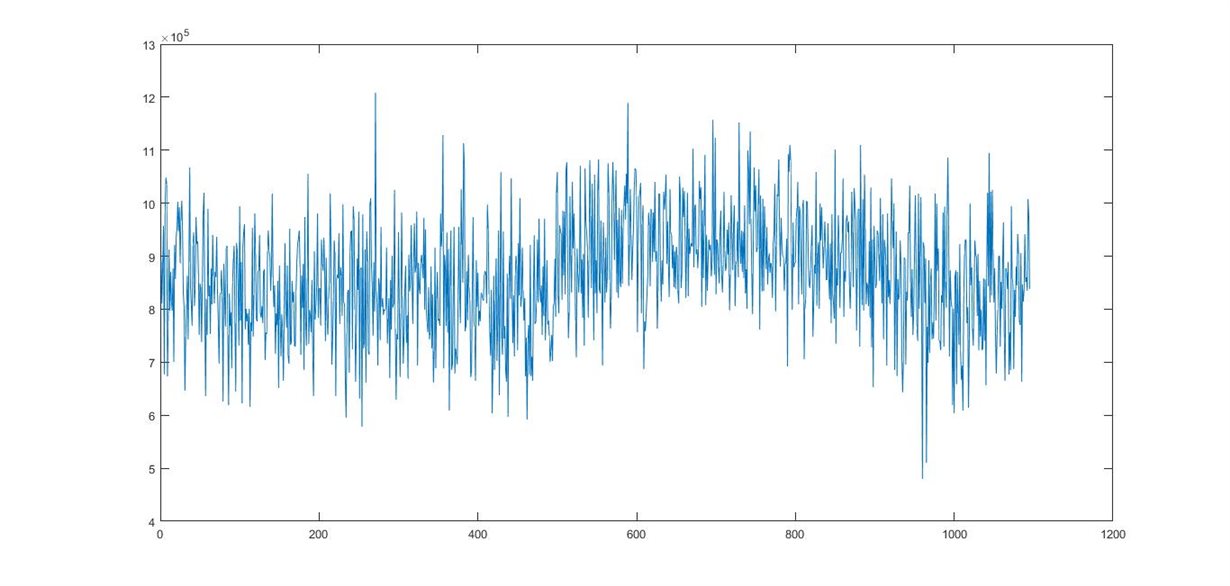

Hello, I have a problem with internal test wave signal. Here is my schematic and matlab plot. Is it possible that I have some issues in shematic?

These are the voltages of ADS1299 chip:

- Vcap1 = -1.36V

- Vcap2 = -1.36V

- Vcap3 = 1.84V

- Vcap4 = 4.64 V

This is how register are configured :

rc=write_byte(CONFIG1,"\96") rc=write_byte(CONFIG2,"\D1") rc=write_byte(CONFIG3,"\E0") rc=write_byte(LOFF,"\00") rc=write_byte(CH1SET,"\05") rc=write_byte(CH2SET,"\01") rc=write_byte(CH3SET,"\01") rc=write_byte(CH4SET,"\01") rc=write_byte(CH5SET,"\01") rc=write_byte(CH6SET,"\01") rc=write_byte(CH7SET,"\01") rc=write_byte(CH8SET,"\01")

I'm clocking out data of only one channel over DRDY event. SPI clock is 250kHz.