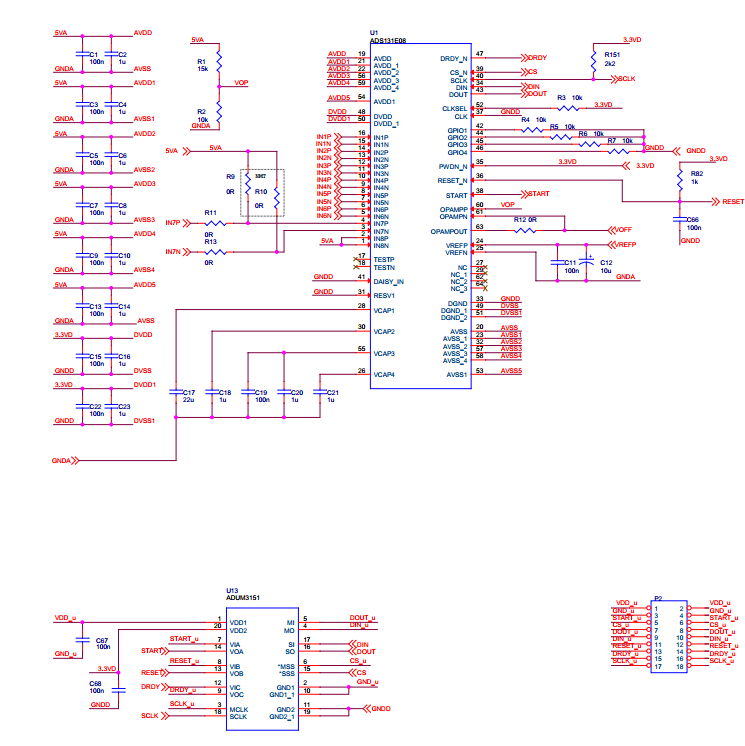

We developed a board with the ads131e08 but we have problems in burst test (IEC 61000-4-4) already at level 1, the data ready pin hangs at level high until we send hardware reset, we saw that if we fix the CS at low level we solve the problem but if we use it to communicate with the device during the test we experience the problem. We are using the Start pin to start the conversion and the RDATA command to retreive the result but the same behaviours is present with the CS fixed at low. Seems that the DRDY is in somehow correlated with the SPI port despite what is written on the datasheet.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.