Hi team,

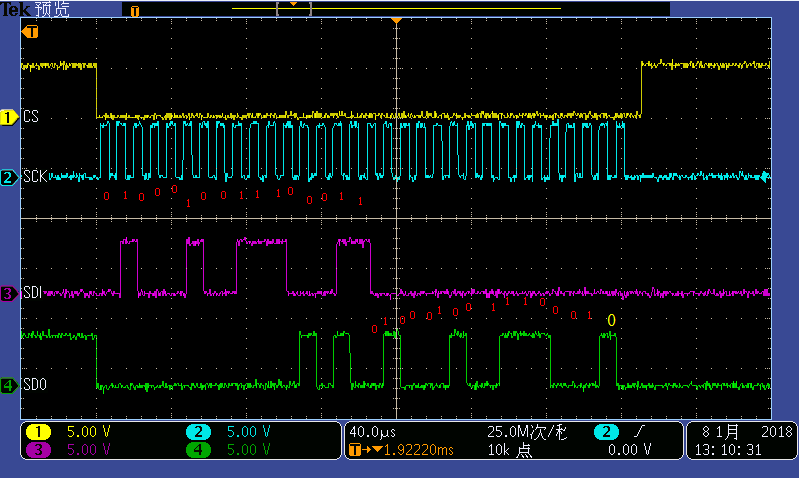

My customer use 2 pcs ADS1118-Q1 in their system, and measuring 6 channel battery voltage in turn. They set the sample rate as 860SPS, and every 5ms to enable 2 single shot conversion.

They using continue mode, and each channel configure as 0x44E3/0x54E3/0x64E3.

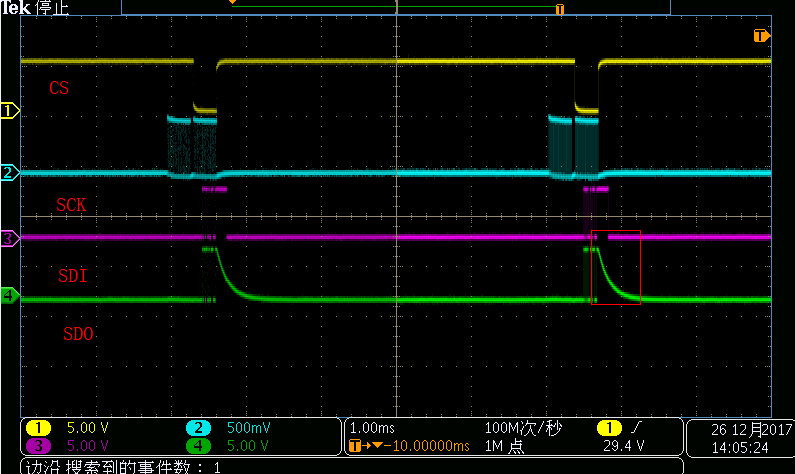

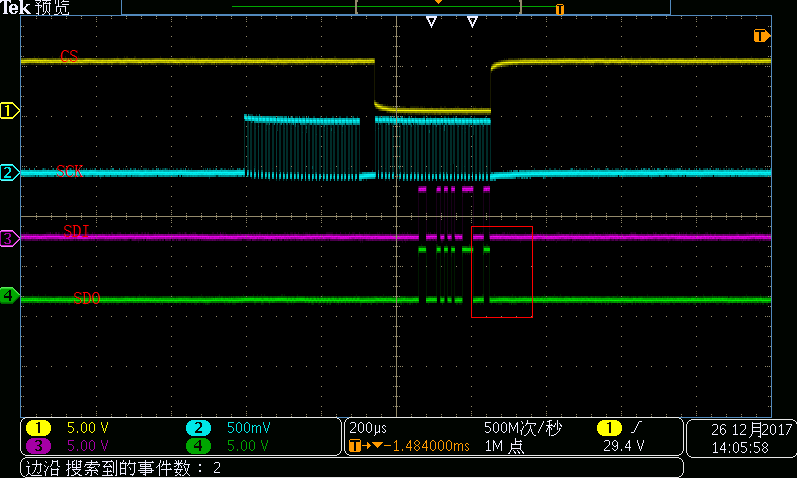

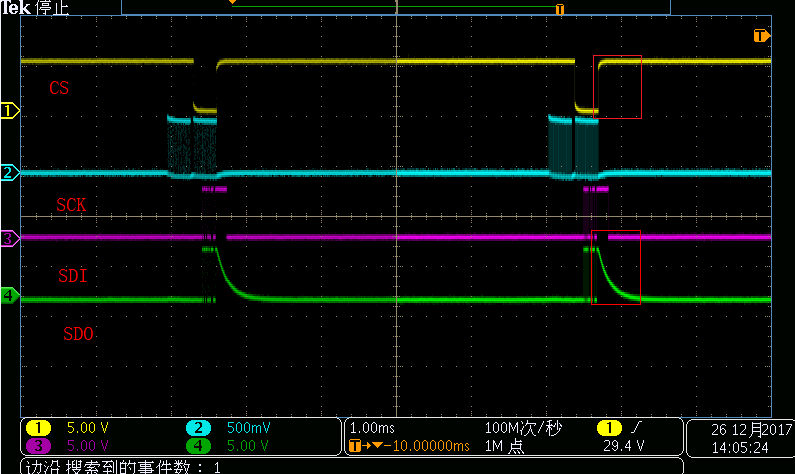

But when the system running at the temperature of 85C, some how it will read back a 0, while the normal read back data should be 200, the result show as below, they encountered 4 times the read back data is 0.

Besides, they found that, the SDO of ADS1118-Q1 will sometimes drop slow, which may cause incorrect conversion result.

Could you please help to check these high temperature wrong read back data issue and the SDO issue?