Hello!

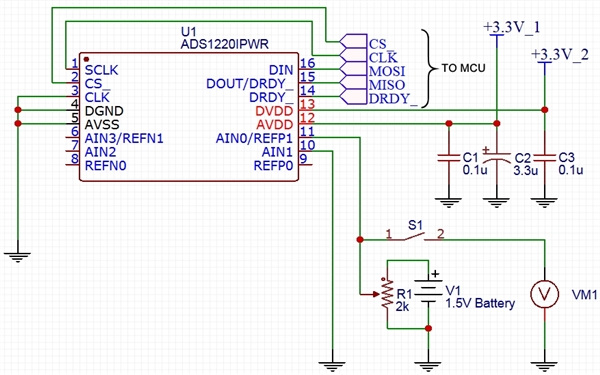

I'm working with ADS1220 - SPI version.

The configurations are default.

I'm sending SYNC command and when data is ready on DRDY signal I'm receiving data and showing it to the terminal. The data is also controlled by logic analyser on MISO pin.

I'm connecting 1.5V battery in differential mode to check system.

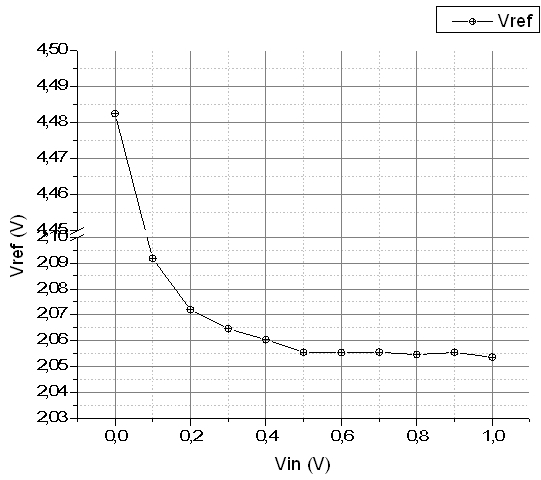

After start all is good: the result is about 6 200 000 in DEC, that is similiar to ~1514 mV. But some time later (some minutes) system starts to show maximum value 8 388 608, that is displaying on logic analyser and on the terminal. When I'm disconnect battery and connect input pins tougether the result is nearby 0. But when I'm connect battery back the result is again goes to maximum. The system works in the same way arfter hard reset again and again.

Do you have any ideas?

Regards,

Vlad

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.