Other Parts Discussed in Thread: INA827, TM4C1294NCPDT

Dear all,

I'm using the ADS131A04, 4-channel delta-sigma ADC, in a strain gauge amplifier design. For my application, 12 channels are required in total but board area is limited so I designed a small stackable board with 4 channels. Three of those boards are plugged into a main circuit board with a TM4C1294NCPDT for signal processing. Reading out the ADCs via SPI works perfectly fine. However, on inspection of the signals I noticed odd disturbances on all 4 channels of some ADCs in the form of low frequency oscillations that occur periodically every couple of seconds. The signal swings up to of 0.5-2mVpp and then fades out again. As the measured signals from the strain gauge amplifiers (INA827) are also on the mV level, such a disturbance is undesirable. Due to its nature, I believe it is also impossible to filter.

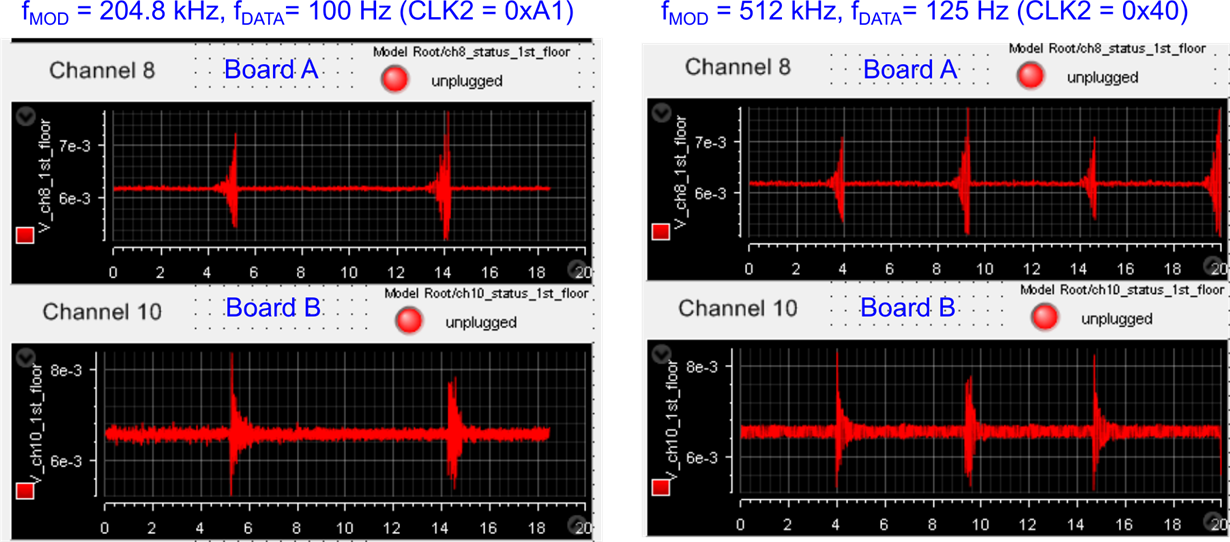

I suspect that what I'm seeing are spurious tones / limit cycles of the delta-sigma ADCs. This is because when I change the modulator sampling rate of the ADS131, the number of disturbances I get in a given period scales accordingly. When changing the ratio of modulator to output sampling rate, the characteristics of the disturbance change. Y-Axis in the figure is in V, time scale in seconds.

Given that my assumption is correct, there still are a couple of effects that I do not understand:

- When plugging in only one of the small boards on the main board, the disturbance never occurs.

- One out of 3 boards does never shows the disturbance for any possible combination of individual boards on the main board.

- Combining one of the "bad" boards with the "good" one leads to a different form of disturbances.

- Combining the two "bad" ones always produces the disturbance I discribed, but the characteristics change a little bit depending on which sockets I use on the main board.

- As you can observe in the pictures, the disturbance is shifted in time between boards and somehow "mirrored"

1) might be explained by the overall noise level changing due to the increase of supply current / capacitance when adding another board.

2) is possibly due to variation in the production process (?)

As for the other effects, I have no idea. Any suggestions/help/comments are greatly appreciated. I need to know the origin of the disturbance and a strategy to avoid it before manufacturing more PCBs that end up being useless for my application.

Input to each positive ADC channel comes from the output stage of a INA827 instrumentation amplifier. Negative inputs are tied to ground. AVCC/AVSS and IOVDD/IOVSS of the ADS131 are tied to the same supply. An (unbuffered) external voltage reference, REF5045, is used. Relevant parts of the schematic are attached for your reference.

Since this is my first post, I hope that I provided all the necessary details. If you need to know anything else about the circuit, system setup, power supply or other stuff, please let me know.