Other Parts Discussed in Thread: ADS1258

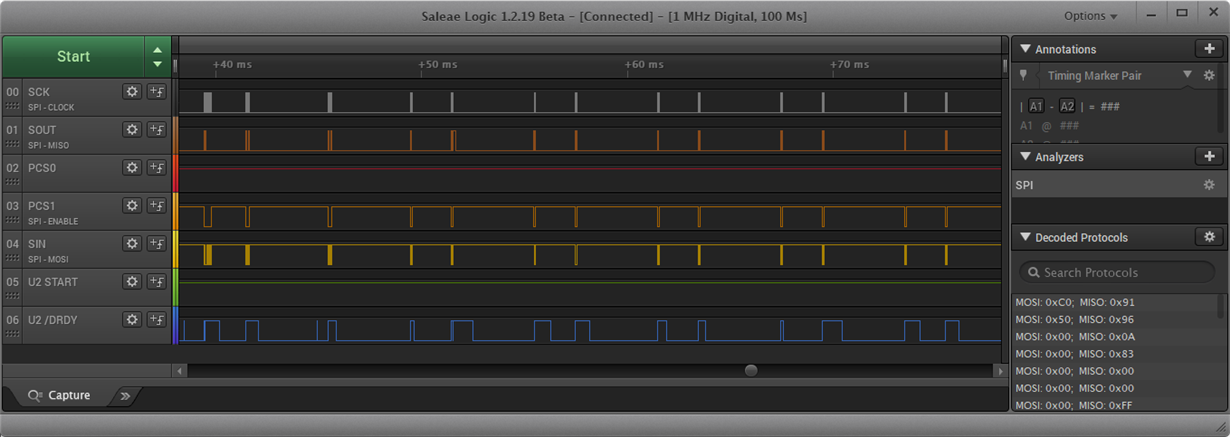

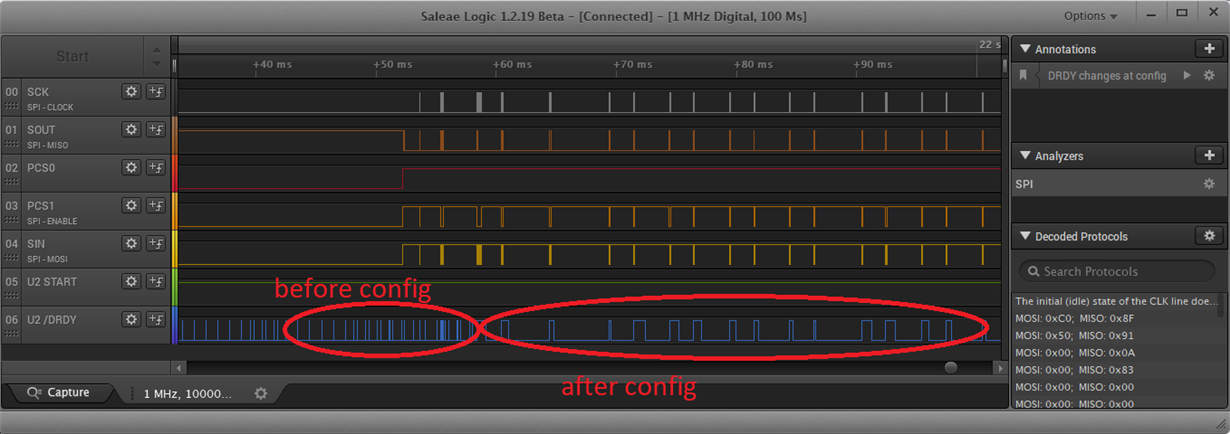

/DRDY not connected so can't use it.

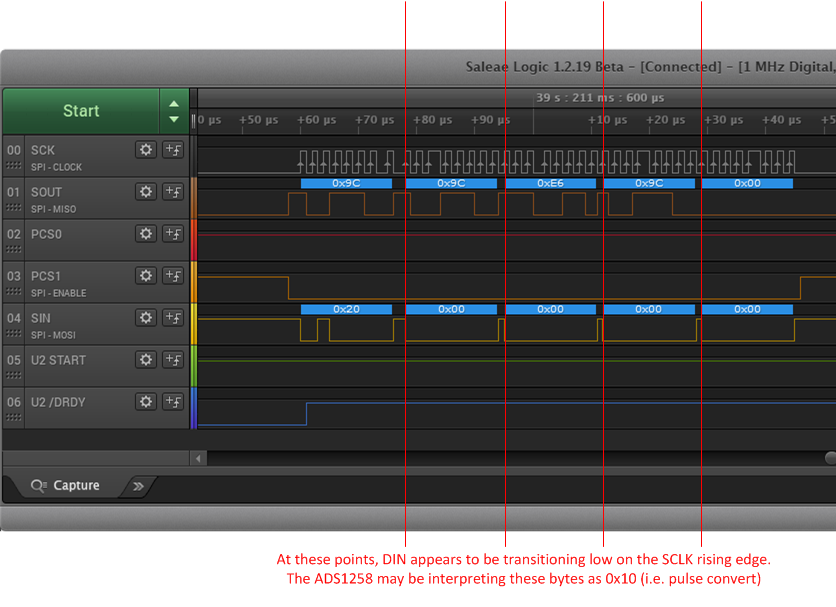

START tied high

simply want to read 16 single ended A/Ds about every 10 msec so trying to figure out how to get close to this behavior

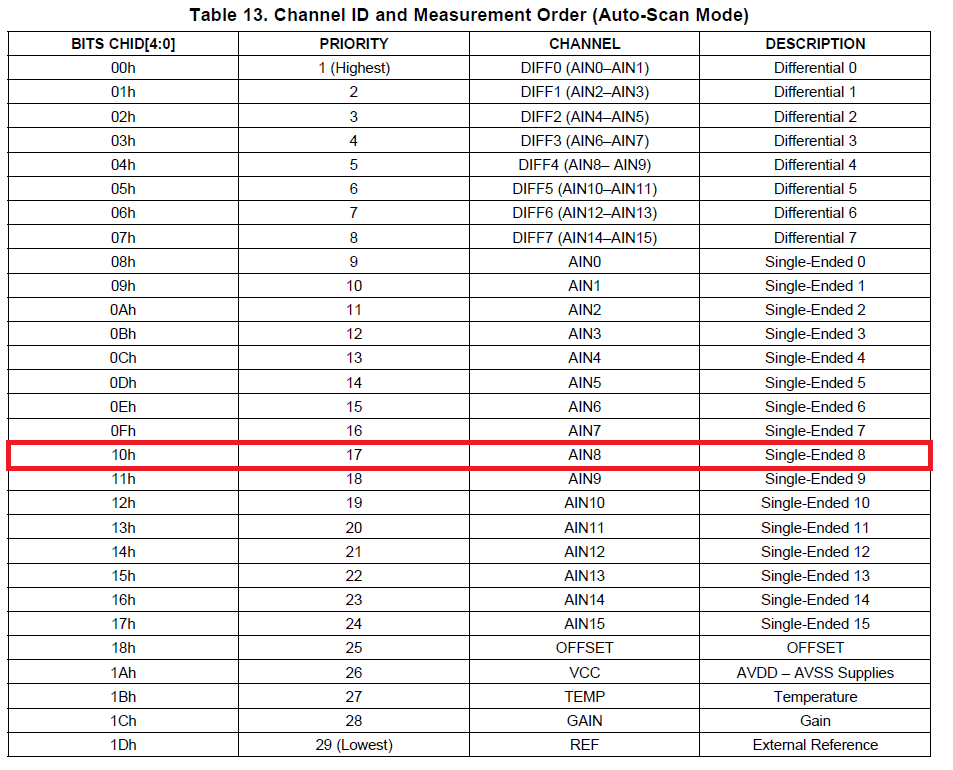

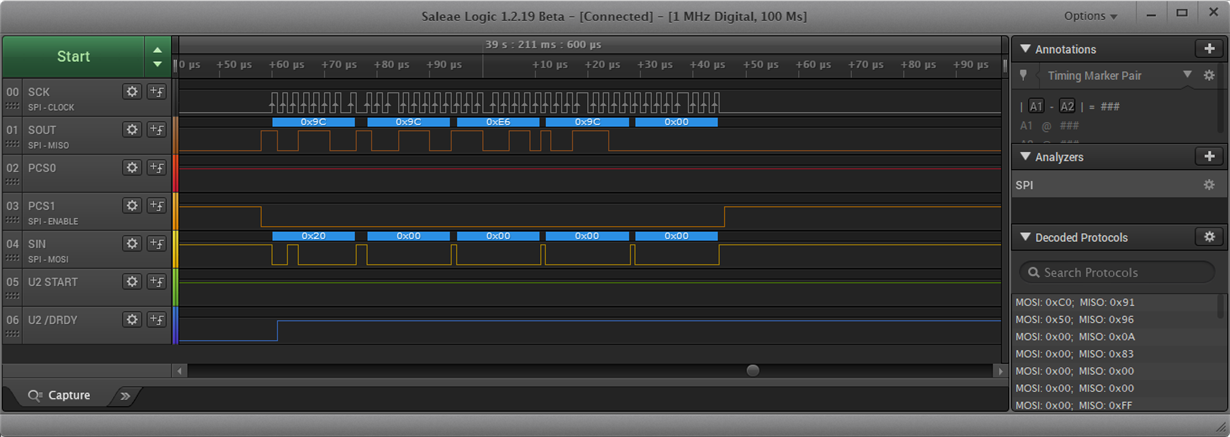

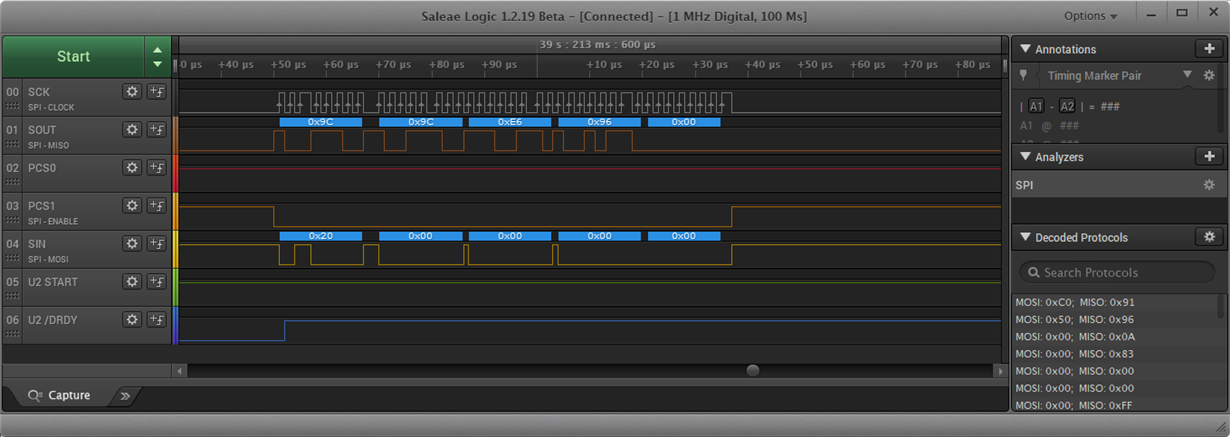

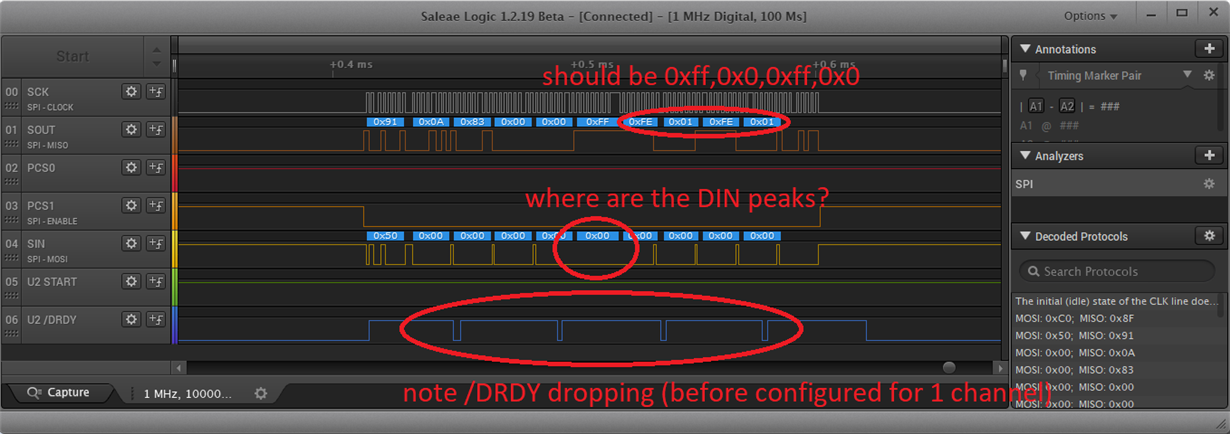

config regs set to (and verified) 0x02,0x70,0,0,0x00,0x01,0,0,0 (status byte on, max delay, only AIN0 enabled)

when I read channel data via register format, I get NEW 16. That's it. Why not NEW 8?

Once I have this one channel working I'll change registers to read the rest as well

I have more questions once this is straightened out