Hi all

Would you mind if we ask ADS7865?

Could you let us know the relationship between AVDD and REFIN.

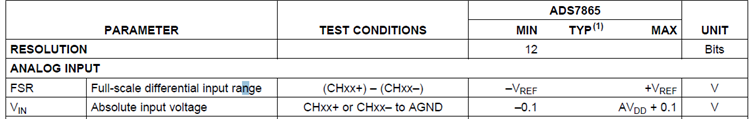

-Analog inputs are single end.

-REFIN is sapplied by external referecence voltage. The customer doesn't use REFOUT.

In case of follows condtion, how will be digital conversion?(Does it effect for digital conversion?)

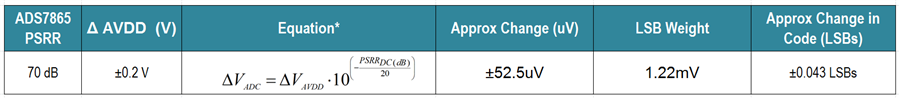

①-1 AVDD=5.2V,VREF=2.5V,Analog input=5.0V

①-2 AVDD=4.8V,VREF=2.5V,Analog input=5.0V

②-1 AVDD=5.2V,VREF=2.5V,Analog input=4.8V

②-2 AVDD=4.8V,VREF=2.5V,Analog input=4.8V

③-1 AVDD=5.2V,VREF=2.5V,Analog input=3.0V

③-2 AVDD=4.8V,VREF=2.5V,Analog input=3.0V

As this qusestion's background, on the customer's ciruit, AVDD accuracy is rough compared with VREFIN.

Therefore, it may occur above conditions ①-1 to ③-2.

Kind regards,

Hirotaka Matsumoto

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.