I have included the schematics for the DAC subcircuit and the power sequecers as a .docx. Hopefully they are readable.

Now to the issue. We are running the DAC8718 in bipolar mode (+/-16.5V) and we have RSTSEL set to IOVdd and #USB tied to GND. With a 4.096V reference on REFA and B (and it is truly a reference that is not tied to any other parts) we see 12.288V on the DAC outputs on boot. If we ground CLR, it will pull the outputs to 0V, but a RST or LDAC cycle will return them to 12.288V. If we boot the device and read the offset registers, they are 0x0000. If we write to 0x999A to them, the voltage on the outputs go to 0V and we can read the same value out of the registers that we wrote in (this seems to indicate the chip believes we are in bipolar mode as well.)

Why isn't the output of the chip on bootup behaving as datasheet seems to state it should (0x999A being loaded automatically). This is problematic as our down stream devices cannot tolerate the 12+V supply.

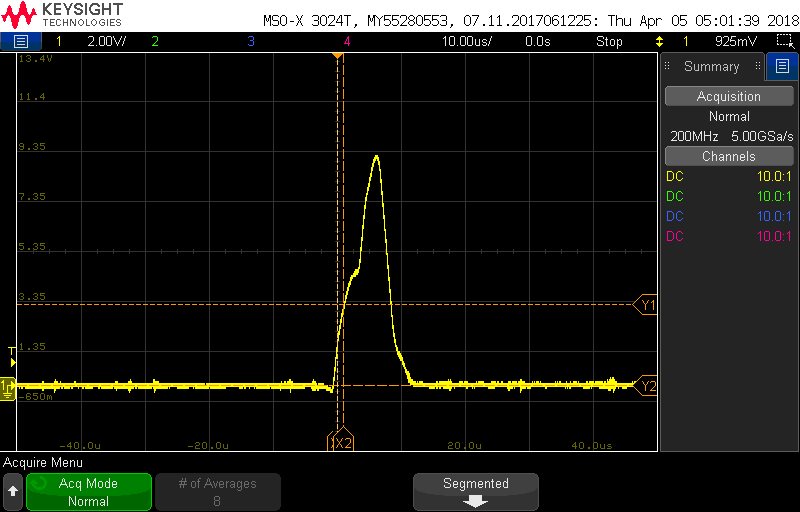

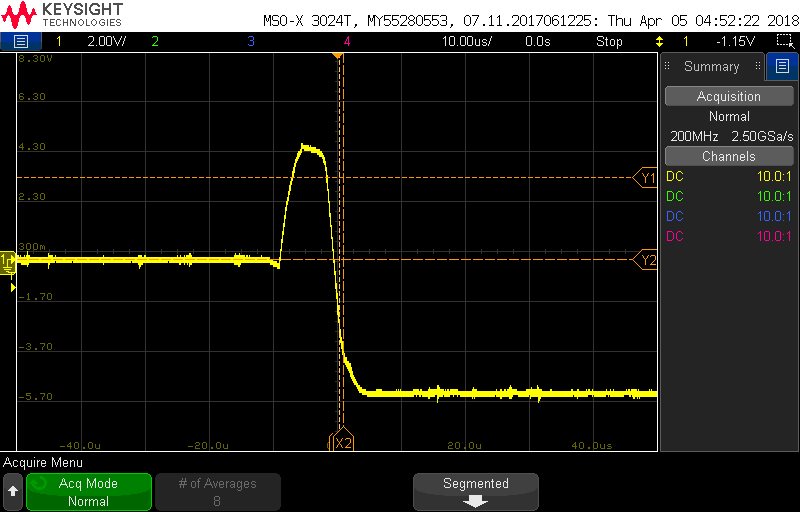

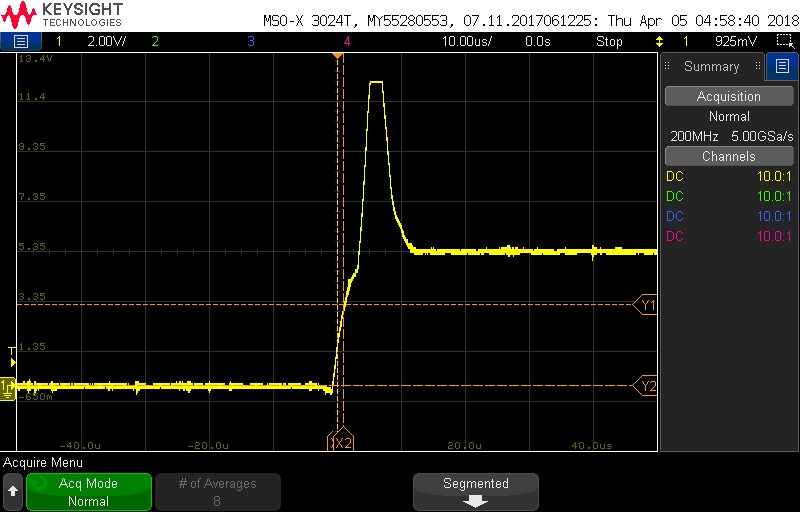

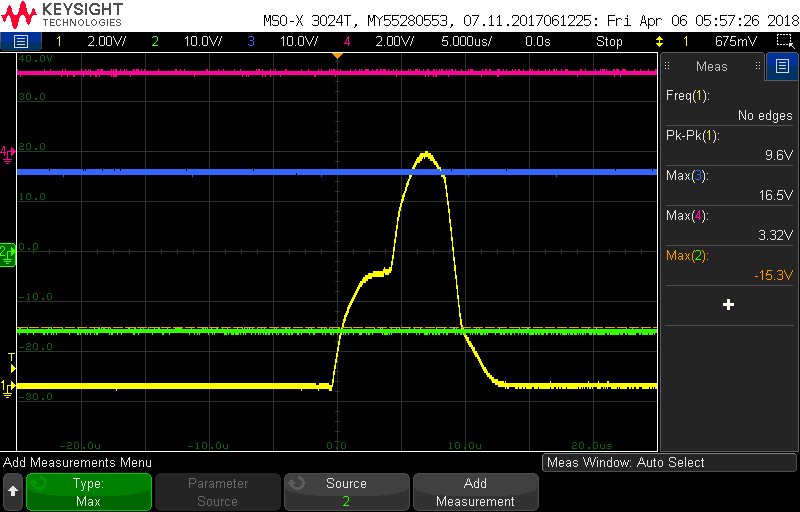

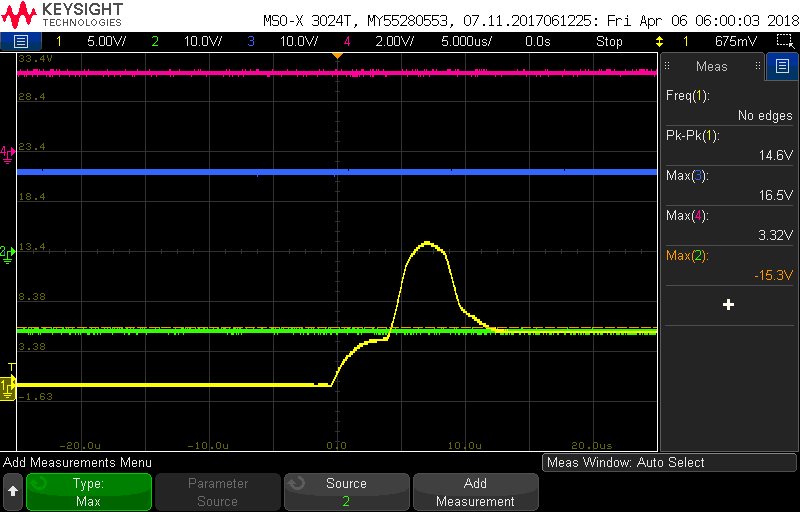

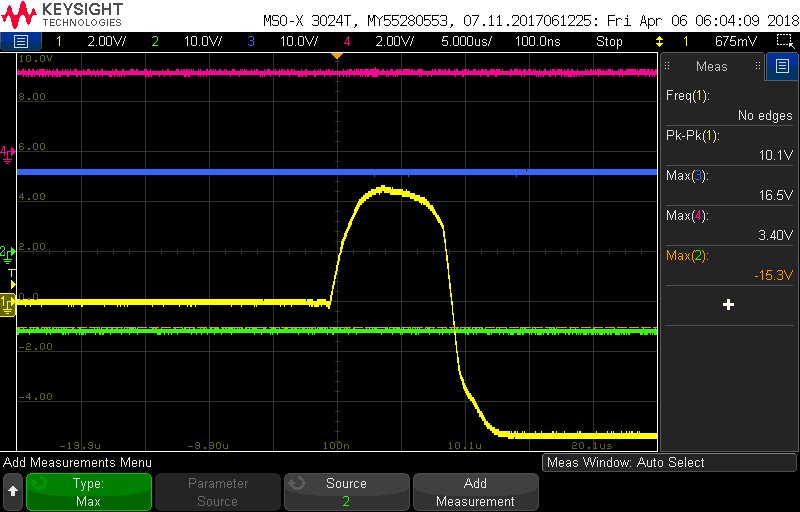

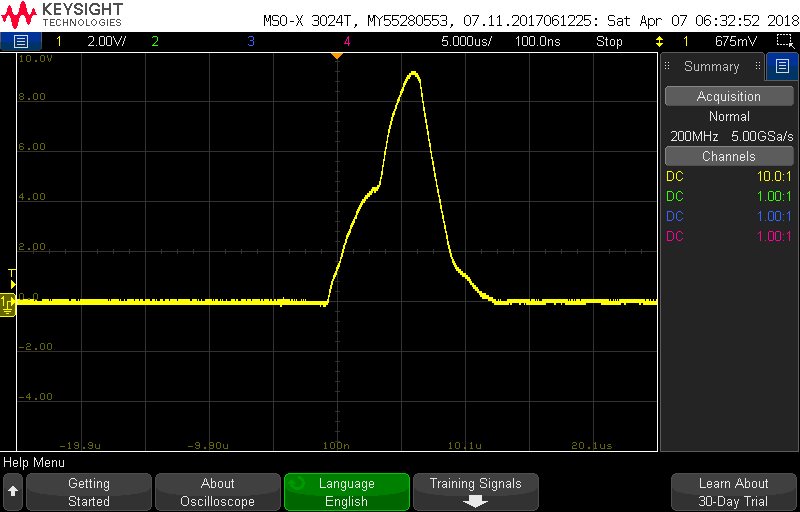

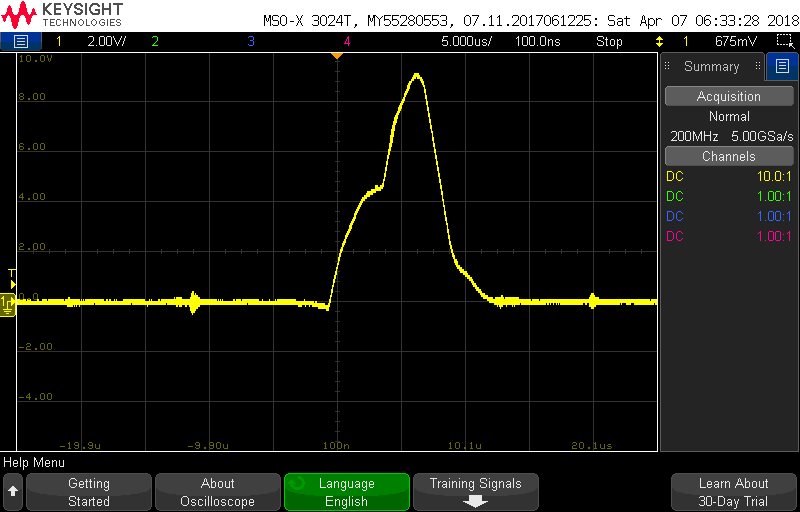

Our power supplies are being sequenced explicitly by the LM3880MF-1AA chips as well. with 3V3(2) on flag-A1 (IOVdd), 5V(2) on flag-A2 (DVdd), 16V5 on flag-A3 (AVdd), -16V5 on flag-A4 (AVss) and our reference on flag-A5 (REF).

I have connected an EVM to bench supplies where IOVdd=DVdd=5V on a power supply, AVdd = 16.5V on a power supply, AVss = -16.5V on a power supply and using the onboard 5V reference with the sequence of 5V -> 16.5V -> -16.5V being turned on and it has the same behavior.

Any suggestions?