Hi,

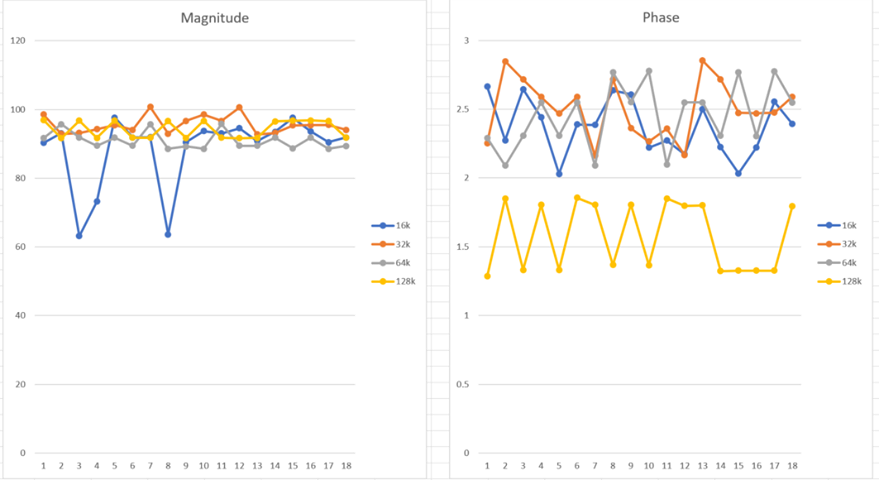

I'm having trouble reading consistent values from the BCM output (ADC_CONTROL_REGISTER2 Addr 0x10).

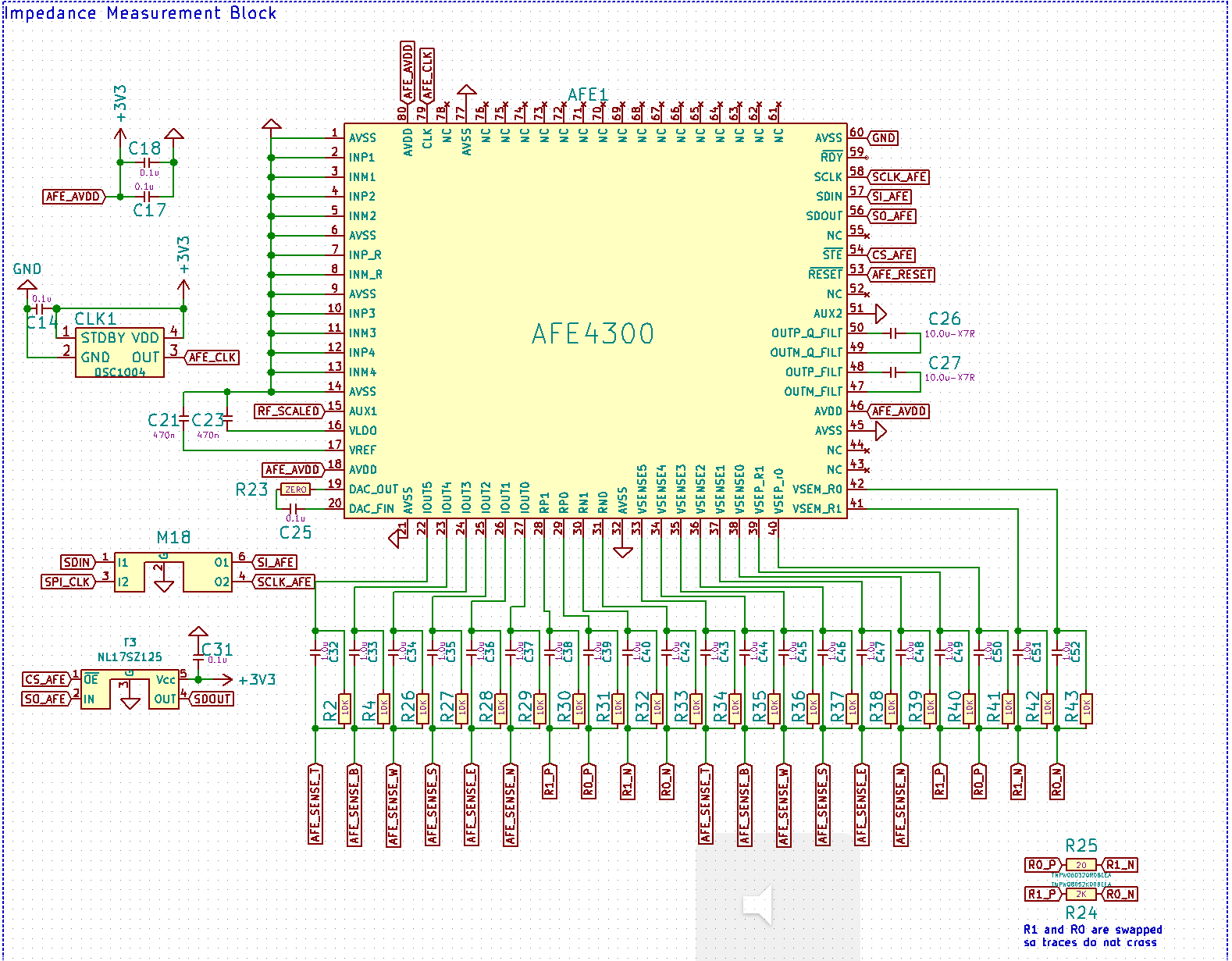

Setting this register to 0x65 -- output for (OUTP_Q_FILT/OUTM_Q_FILT) -- returns consistent values on multiple measurements at the same frequency (i.e. 0xff13, 0xff19, etc.), but when setting the register to 0x63, the measurements return very different (i.e. 0xe9e, 0x2bac, etc.). However, the circuit for each is consistent/same.

Any ideas on what might cause this to occur? Appreciate any help and direction.

Thanks!