Dear TI,

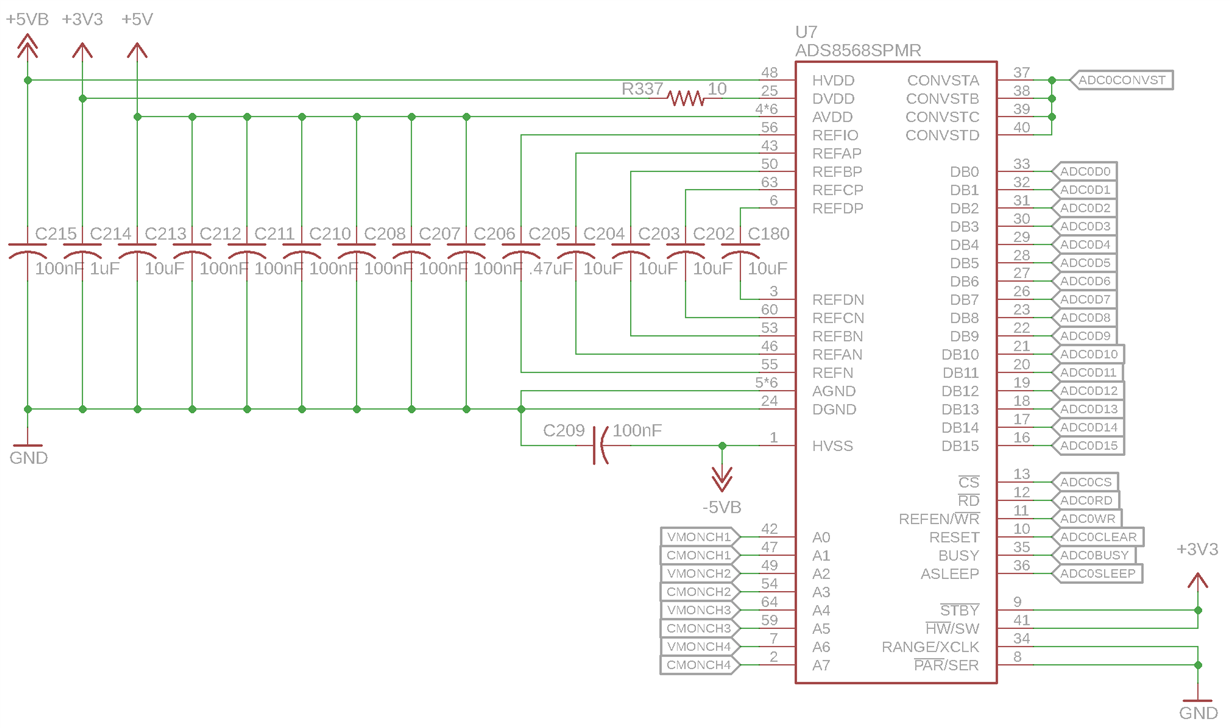

I have attempted to design a circuit for the ADS8568 and would appreciate a review and design guidance.

My design goal for this is to use the parallel interface to a microcontroller and sample from 8 channels simultaneously at maximum speed. Input signals are in the range 0-3.3V centered at 1.65V.

My main worries:

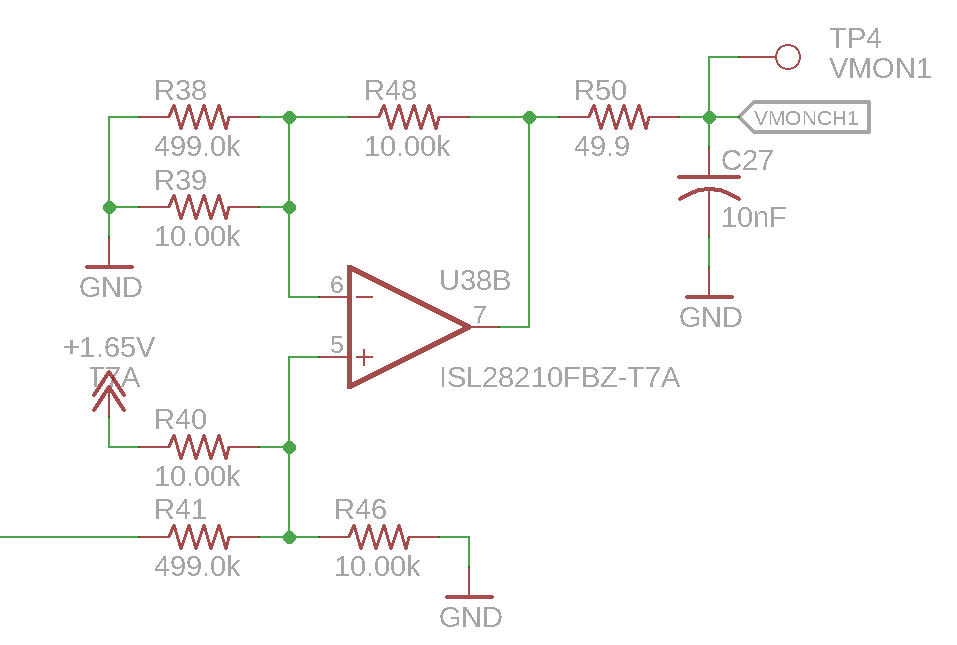

- On each analog input, I have this circuit which only has 49.9 ohms of resistance and a 10nF capacitor. I will probably replace the 10nF capacitor with 4.7nF to get the -3dB frequency above the sampling rate, but would appreciate any recommendations. My understanding is that this amplifier must be powered after the ADC. Should I add an extra resistor to limit current into the ADS8568? Is the extra input filtering capacitor unhelpful due to the internal capacitance?

- What power sequencing is required? Right now my ±5VB supplies become active two seconds after AVDD and DVDD, is this okay?

- Can I operate this device with ±4-VREF and a 2.5V reference from this ±5V HVDD/HVSS supply or do I need more overhead?

- My read is that the RESET line needs to be held low in normal operation. This is flipped from most RESET lines so I wanted to confirm before hardwiring.

- Should I instead use a choke on DVDD rather than a 10 ohm resistor?

- Should there be a 10uF capacitor in addition to the 100nF capacitor for HVDD and HVSS?

- I am going to use the PM version without the pad underneath. Are there recommended ground plane connections in this situation? Should I avoid running any traces under the chip and leave that as a continuous ground plane?