Other Parts Discussed in Thread: ADC12J4000EVM

Hi everyone,

I'm using DAC38RF82EVM to interface with a Virtex 7 FPGA board.

The DAC is operating in the dual DAC (16bits) mode with 3.2GSPS, 2× interpolation. I succeeded in my previous design without getting any alarms in DAC38RF82EVM GUI.

However, after I incorporated a ADC12J4000EVM in this project and made another project, some alarms DAC38RF82EVM GUI appeared. Although the DAC has output and it looks correct, I'm afraid unpredictable problems may happen to my future design since there are some alarms.

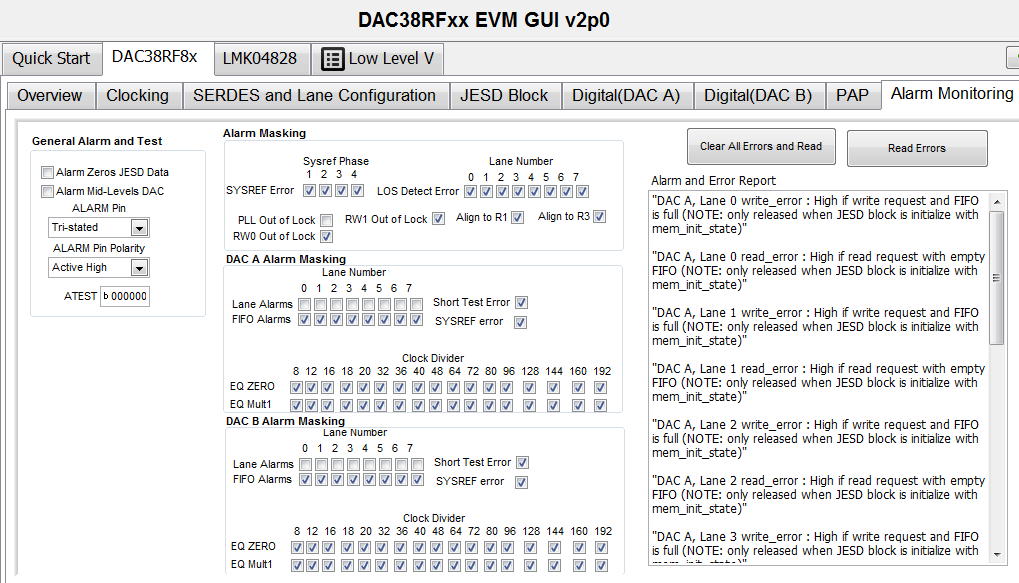

The alarms are as follows.

"

"DAC A, Lane 0 write_error : High if write request and FIFO is full (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 0 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 1 write_error : High if write request and FIFO is full (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 1 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 2 write_error : High if write request and FIFO is full (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 2 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 3 write_error : High if write request and FIFO is full (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC A, Lane 3 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC B, Lane 4 write_error : High if write request and FIFO is full (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC B, Lane 4 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC B, Lane 5 write_error : High if write request and FIFO is full (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC B, Lane 5 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC B, Lane 6 write_error : High if write request and FIFO is full (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC B, Lane 6 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC B, Lane 7 write_error : High if write request and FIFO is full (NOTE: only released when JESD block is initialize with mem_init_state)"

"DAC B, Lane 7 read_error : High if read request with empty FIFO (NOTE: only released when JESD block is initialize with mem_init_state)"

"

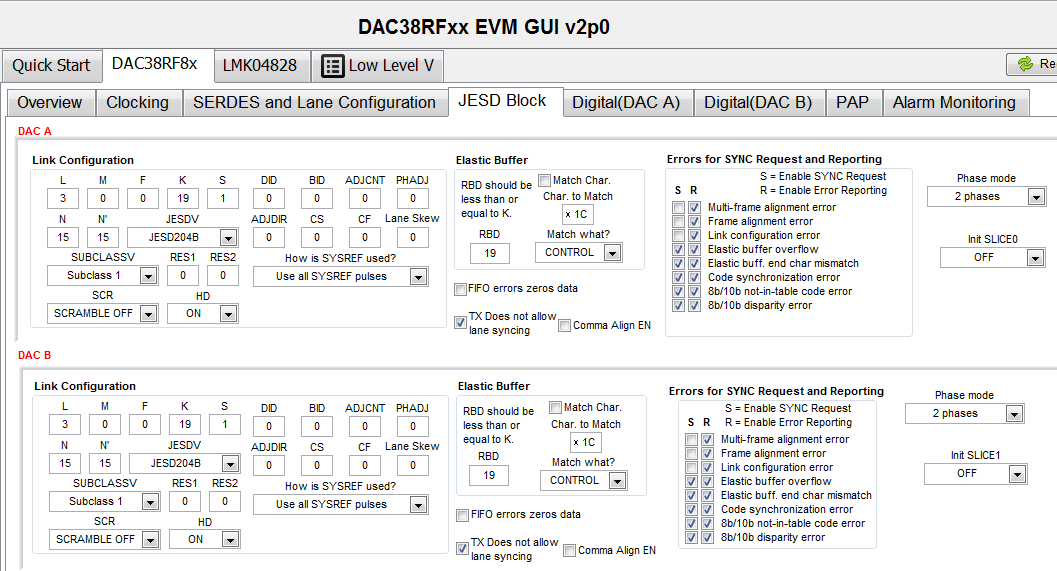

Here are the screenshots of JESD configuration and DAC alarms from DAC38RF82EVM GUI.

The link parameters of the JESD204B IP core in Vivado project is shown as follows.

Can any one tell me what I should do to debug this project?

Thank you very much.

Regards,

Tong