Hi, everyone!

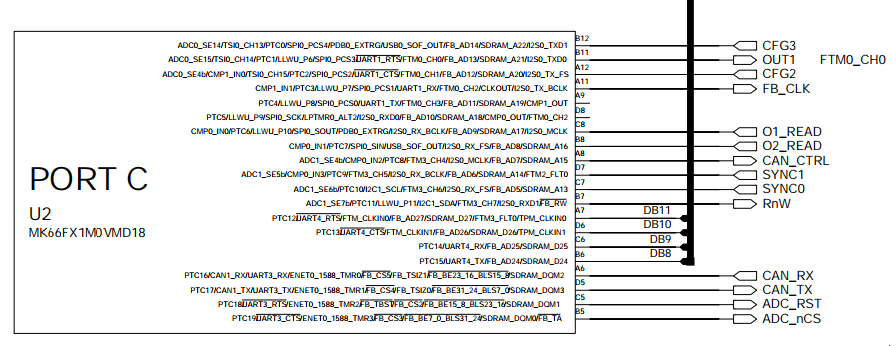

I have a custom board with an ADS8568 configured in hardware mode. I trigger the coversion with a PWM generated from a microcontroller; all 4 CONVST pins receive the same signal.

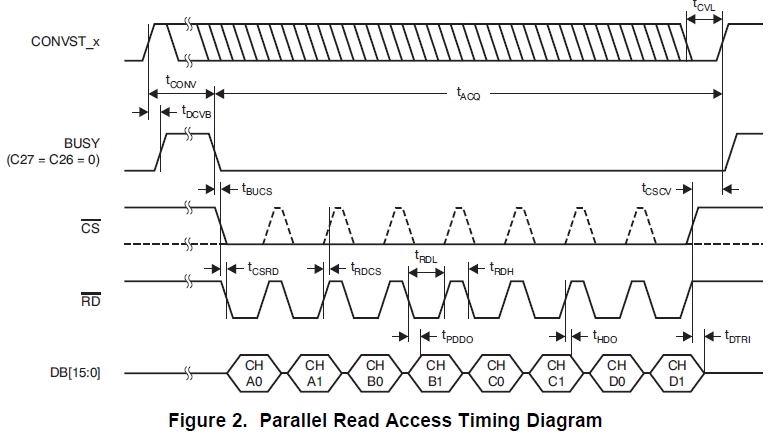

In my firmware, I check the delay between two consecutive BUSY falling edge, and I've noticed that sometimes the delay is way lower than the PWM period.

Analyzing the problem with an oscilloscope, I've noticed that there are spurious BUSY signals not relative to any CONVST (the CONVST is clean and steep, so it is not due to noise on this signal). Debugging the problem I've noticed that the occuence frequency of these "spikes" is relate to the read frequency. As an example, reading all 4 channels, I'll get a spurious busy once every 10 seconds. If I don't read anything after BUSY falling edge, I'll get no spurious BUSY.

For testing purpose I'm working with a slow CONVST (50Hz). As said, ADS8568 is in HW mode, parallel interface.

Any idea?

Thanks