Dear TI team,

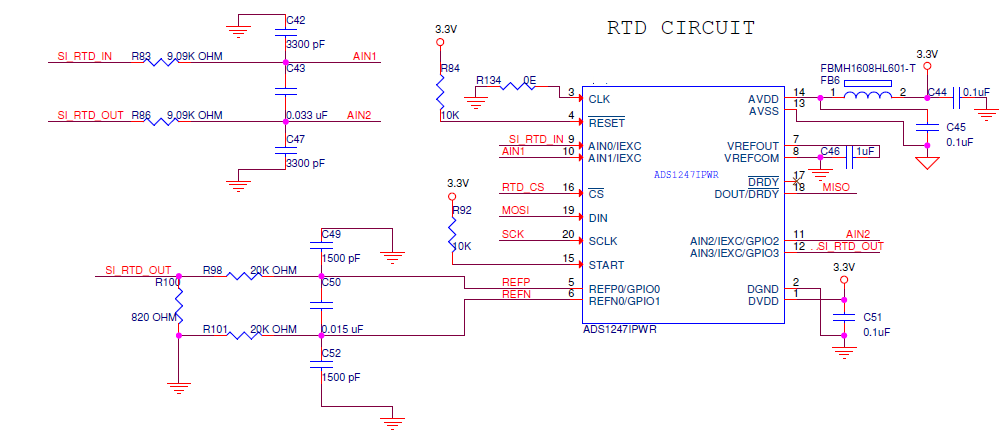

I am communicating with ADS1247 using ATmega128 (SPI mode1, 1MHz clock, MSB first).

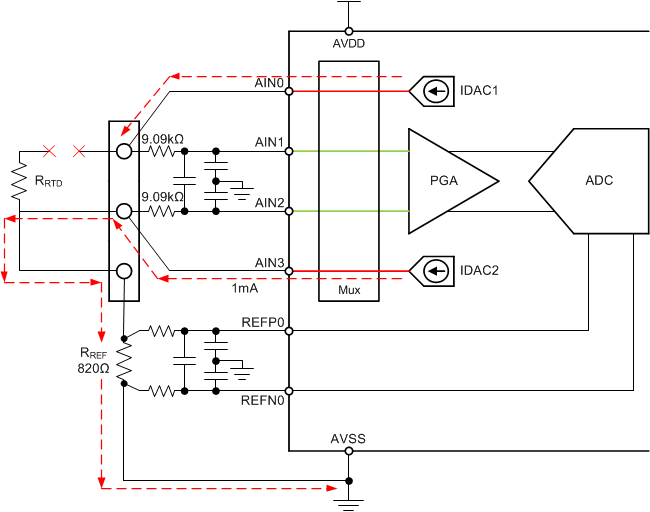

I have used 3 wire design example as per the datasheet and also done register configuration as in datasheet.

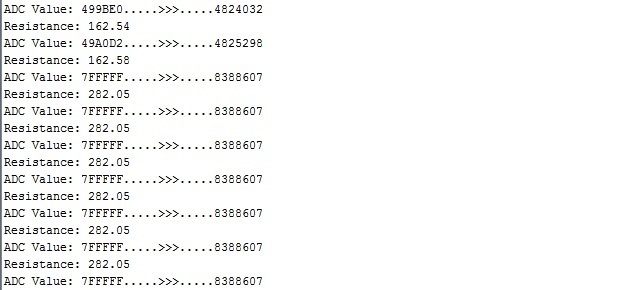

I was getting only 7FFF (Sending RDATA, NOPs & reading data in a loop) . Also the voltage across RREF(R100) is 820 mV.

I tried changing gain & sampling rate, SPI clock rate settings. But the result is same :(

Then i started reading data by checking DRDY status (Configured for DOUT/DRDY). Now I am getting constant value (not correct), but varies after every power on/reset.

Reference voltage across 820ohm is still 820mA.

Thanks,

Sushma