Other Parts Discussed in Thread: ADS52J90, LMK04826

Hello

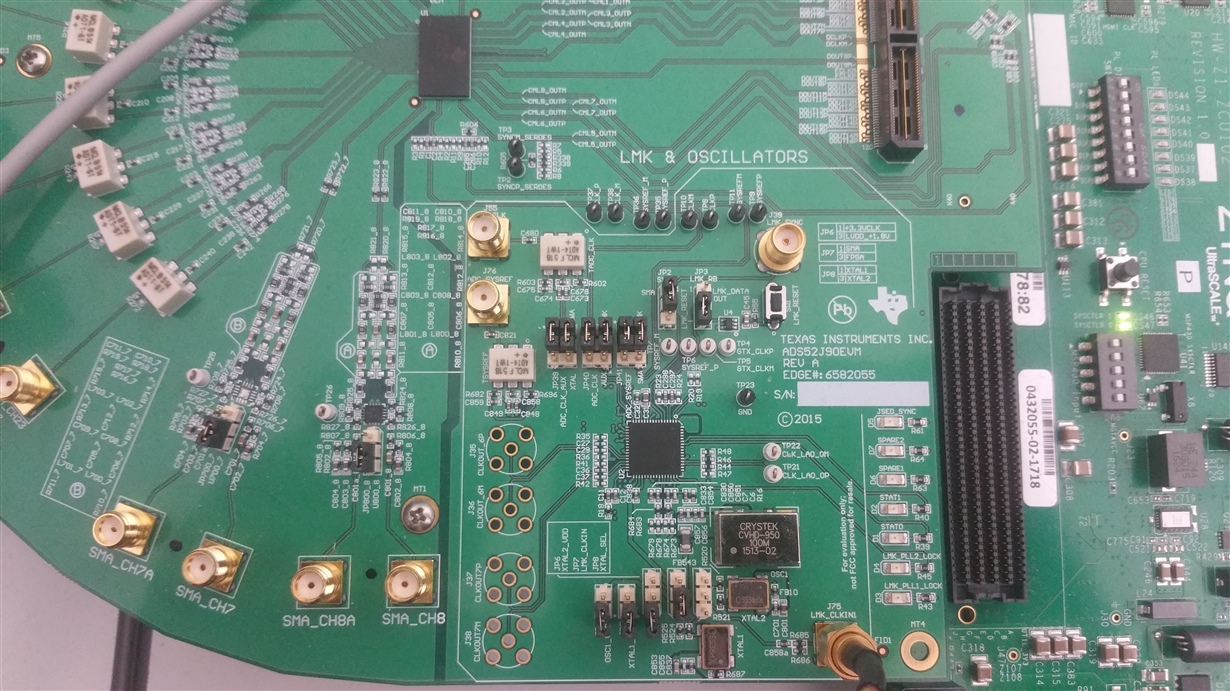

I am using TI's High speed ADC board ADS52J90EVM. I am using Xilinx Zynq Ultrascale+ board to read ADC samples But before this i wanted to see if the adc is configured properly and is giving out all the required signals. Therefore i have connected ILA debug core to the ports of ADC.

I can see Sysref Signal periodically repeating, Ref Clk is also working. but the FPGA CLK signal is low all the time.

I am using the quick start jesd configuration. (please see the attached file)

Could you tell me what could be the issue ?

Thanks alot for assistance.

Best Regards

RizwanADS52J90_16ch_SINE_4L_12x_12b_GBLCLKDIV1_FSDIV3_SYSREFDIV24_20x.cfg