Other Parts Discussed in Thread: , ADS1220

Hi,

I would need advice on some behavior regarding system monitor readout during overvoltage on analog inputs.

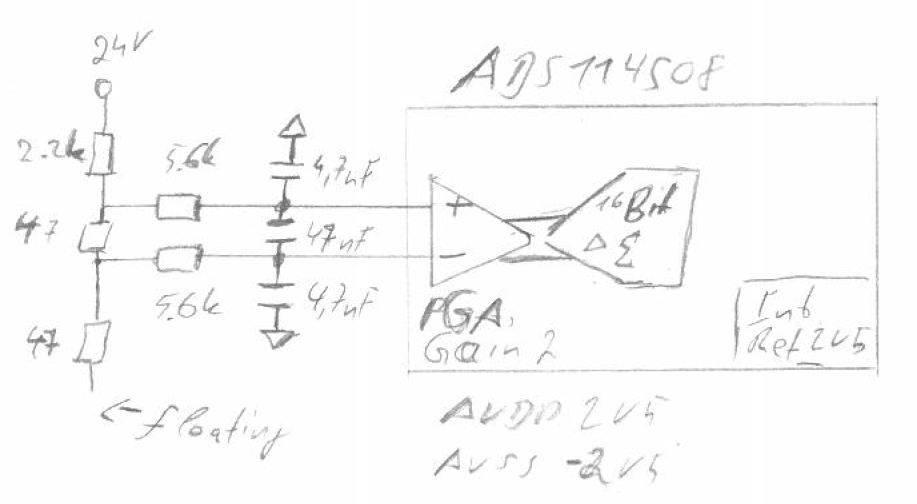

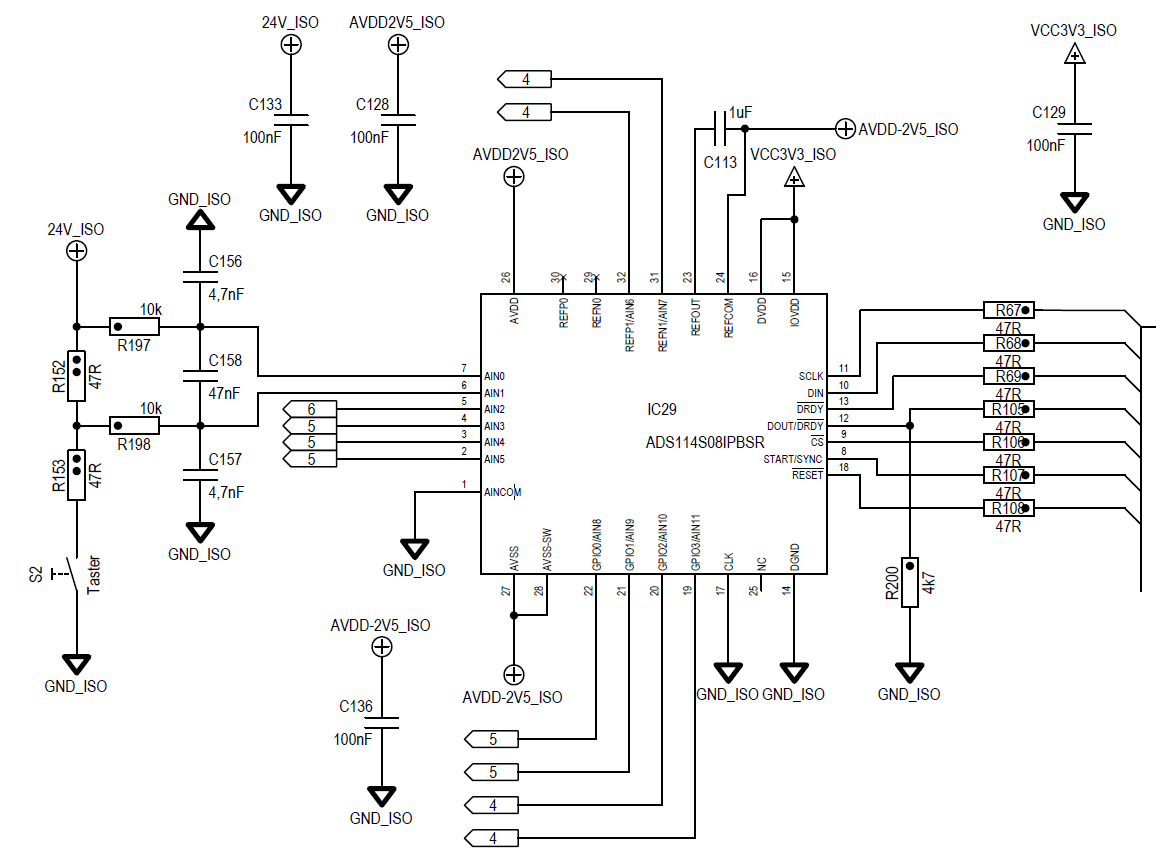

My setup is as follows:

ADS114S08 with AVDD = +-2.5V, DVDD = 3,3V

RC low pass filter on all analog input pins with 10k Ohm resistor in series.

When 24V is applied on two analog inputs 3mA(total) input current is flowing.

The device’s overall operation seems normal (inputs are at FSR), except the system monitor value for AVDD and DVDD indicates 0. The internal temperatur value is dropping(not 0).

I would not expect any change there. Can this be caused by an electrical problem?

I would appreciate any help, because after lots of software debugging I am running out of ideas.

Best regards

Daniel