Other Parts Discussed in Thread: DAC3484, DAC38J84

Hi team,

My customer is using DAC3482 in a signal generator board. For some specific board, we found a strange phenomenon. At first, the DAC3482 works well. After it running for several minutes, we power down the board and power it up again, we found the DAC3482 output is lost. The input clk and FPGA input data are all existing. When we manually cool down the device and restart it, the DAC3482 output shows up again. This issue happend on 3 boards out of 10 boards.

The input clk is 500MHz. Interpolation=2. Data rate=500Msps. fdac=1GSPS

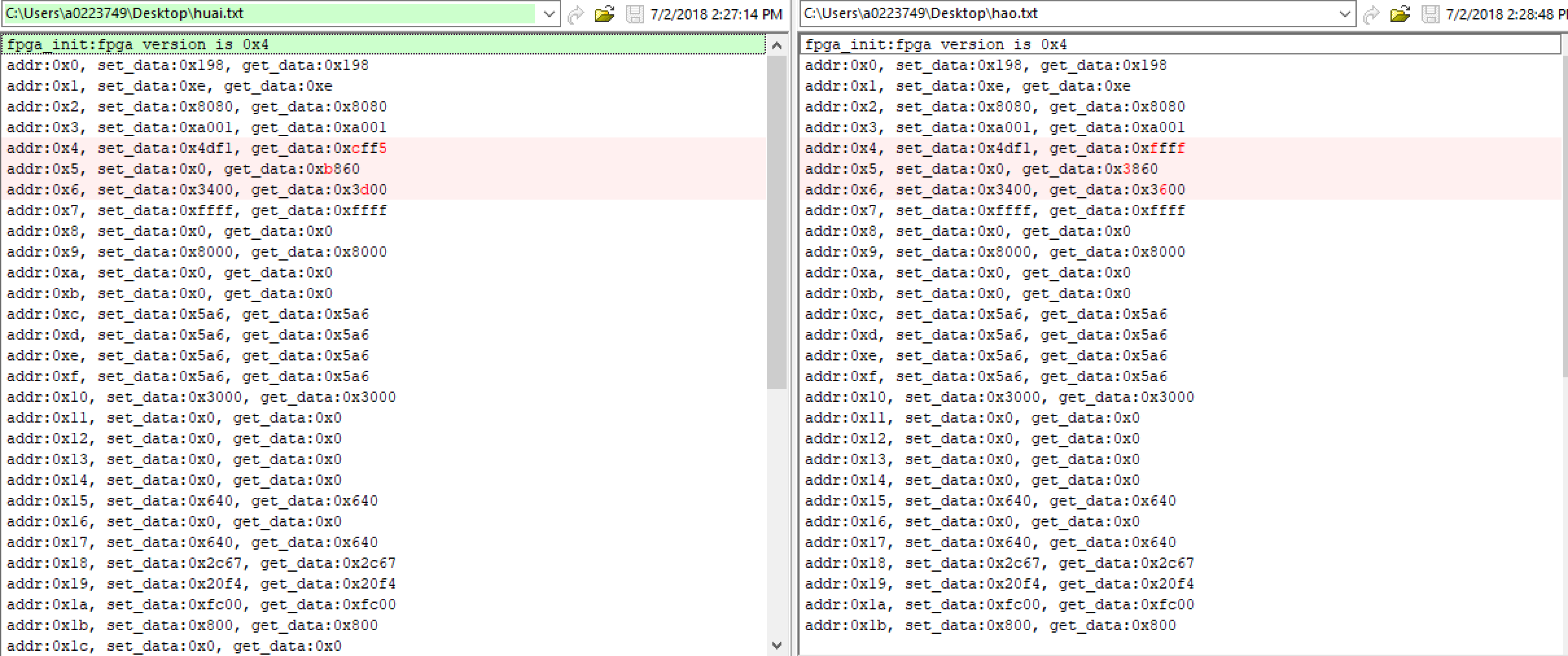

We read out the reg values as below. The left column is read out when there's no output. The right column is read out when there is output.

For reg 0x4, the value is different, but customer didn’t enable the “iotest_ena” in reg1. So why the value is different? Is this related to the output lost issue?

For reg 0x5, even in the right column(the DAC works well), the bit13-11 are all 1 which means “FIFO pointer collision alarm”. Do you think it is normal that this alarm happens when DAC3482 works well?

What’s more, in the left column, the bit 15 is 1 which is different from the right column. This means the alarm_from_zerochk. Do you think this is related to the output lost issue? If it is, how can we get rid of this alarm?

For reg 0x6, it means the temperature value read out. We read out the right column value after cooling the device down. So the value in right is smaller than left which is reansonable. But even when the output is lost, the tempertaure is not that high.

Hope you could help find out the root cause of the output lost issue. If you need more test results, please let me know. Thanks.

Best regards,

Wayne