Dear Sir,

We are trying to integrate ADC12DJ3200EVM, REV-A board with our Custom designed Virtex-7 690T FPGA based board.

We are using FMC+ to FMC interposer for interfacing ADC12DJ3200EVM Eval board with Virtex-7 690T board.

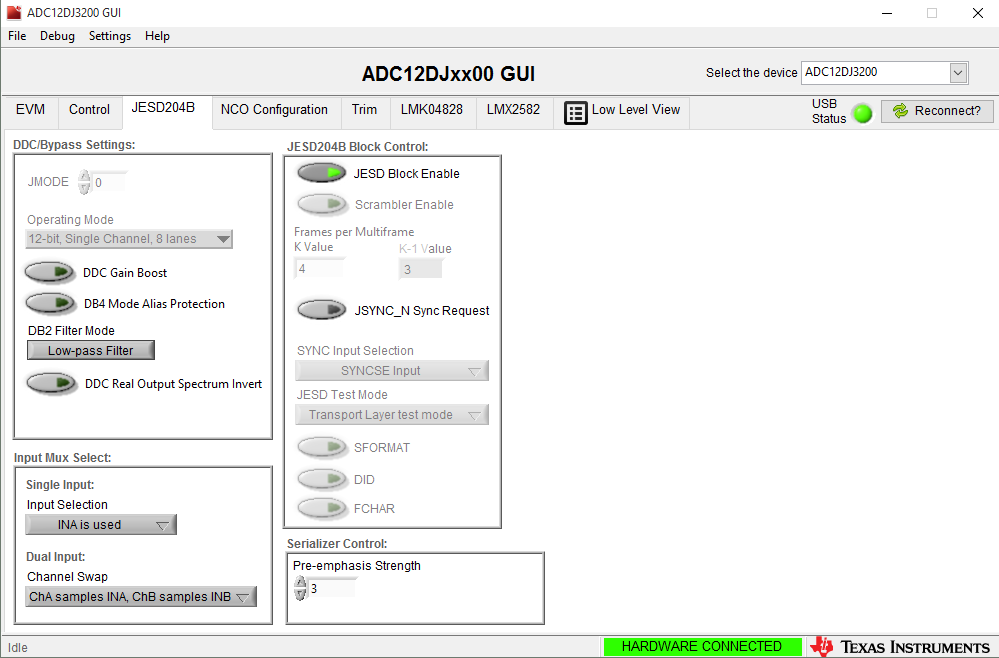

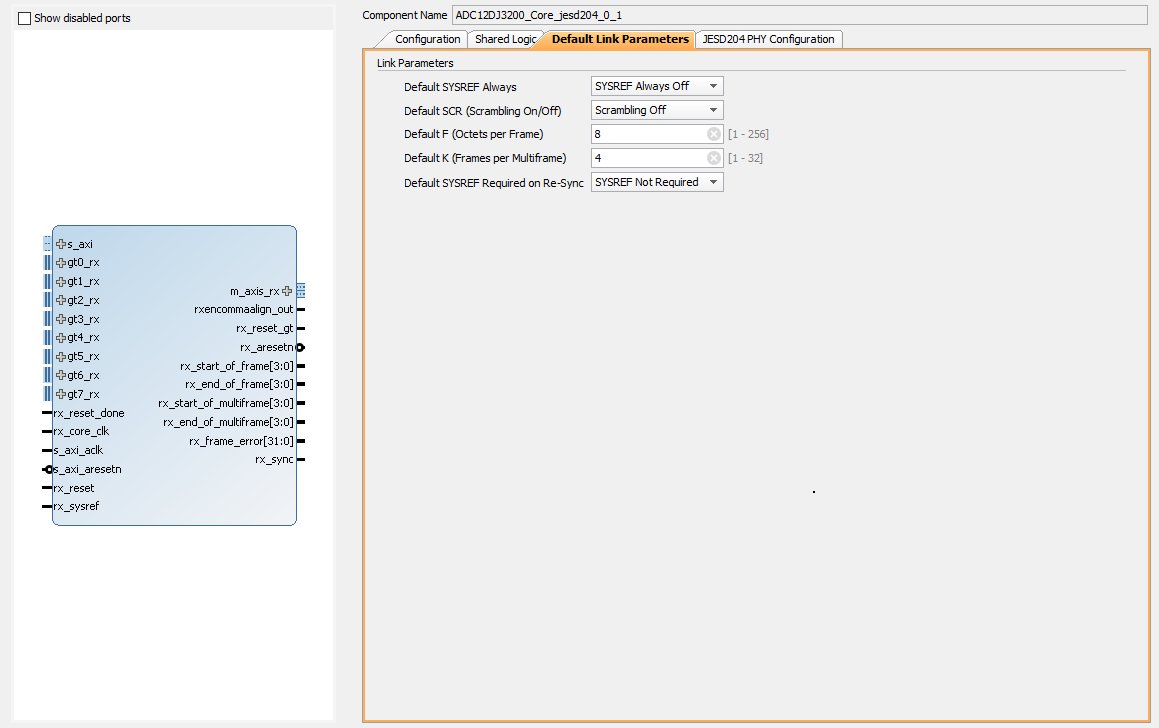

We have used Xilinx IP JESD204B PHY and JESD204B for interfacing ADC12DJ3200EVM to Virtex-7 FPGA. We have enabled Short Transport Pattern Test Mode from ADC12DJ3200 GUI

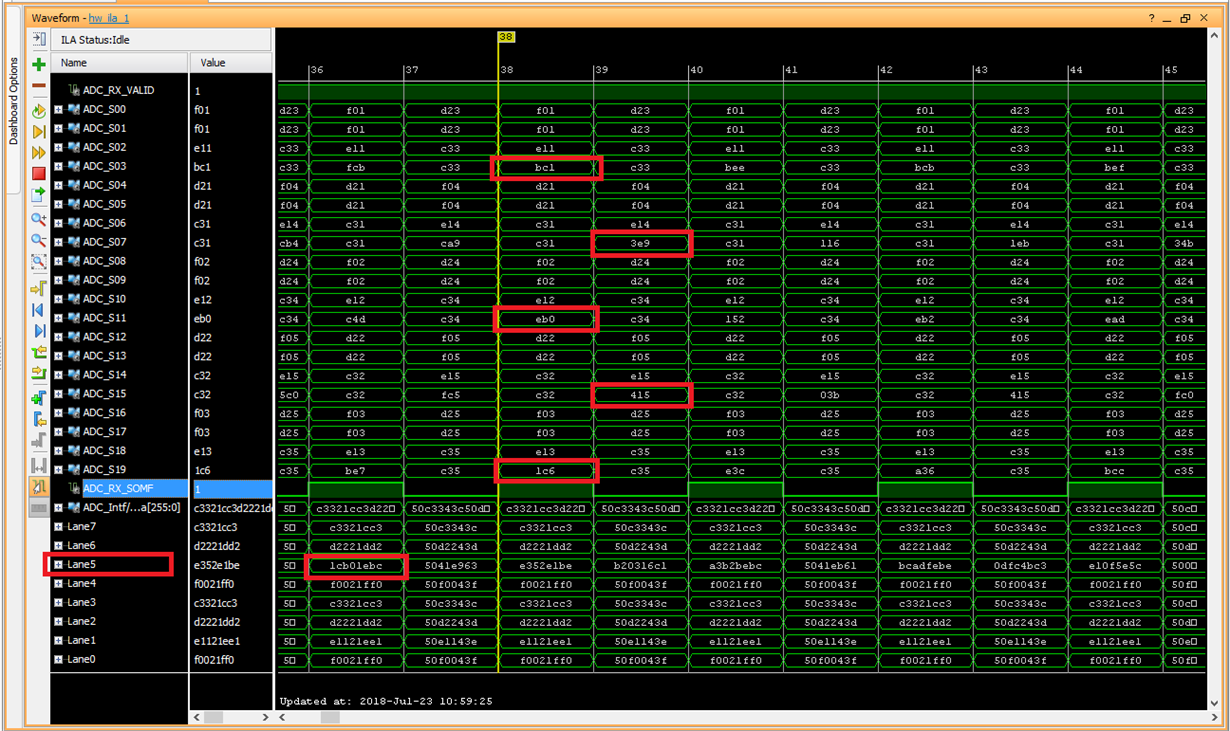

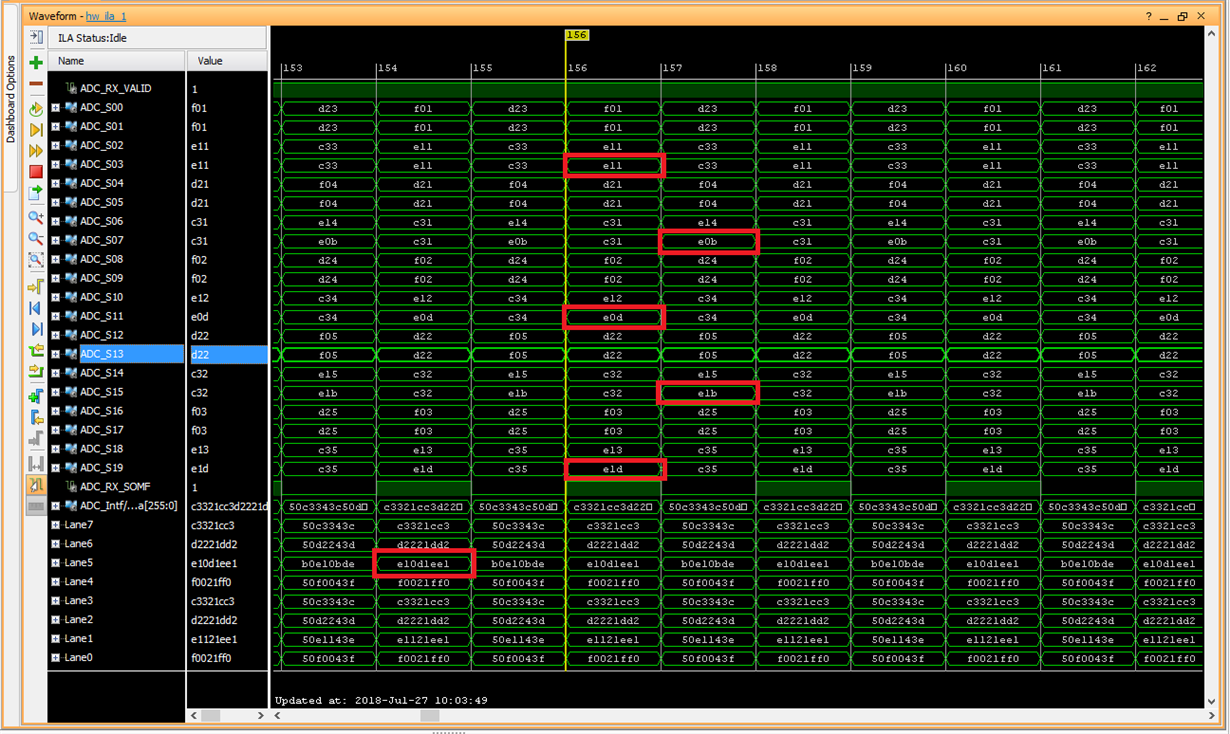

for verifying the Interface between ADC12DJ3200EVM and Virtex-7 FPGA. We are observing mismatch in the sequence received as compared to sequence stated in Table-40 of ADC Datasheet.

We have attached a snapshot of the received data for your reference. There is a mismatch or data corruption in Lane5 only. Others Lane are working fine.

We have programmed ADC12DJ3200 in JMODE0 and Scrambler is On. We have also changed the sampling frequency from 800 Msps (3.2 Gbps) to 2500 Msps (10 Gbps), but still the results are same.

Kindly Clarify,

1. What could be possible reason for this kind of mismatch ? Have u observed anywhere this kind of Issue ?

2. Do I have any option to change the ADC TX Parameter like TX Swing, De-emphasis ? I have changed Pr-emphasis values also, but it didn't help.

Thanks,

With Regards,

Santanu