Hello,

About SPI specification

Regarding to SPI specificationon DAC084S085, my customer is asking a question.

(Question)

(1)

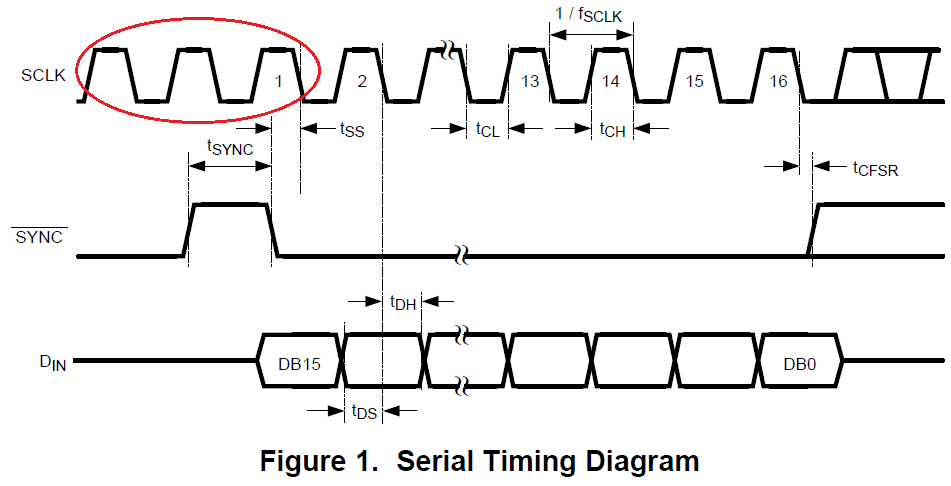

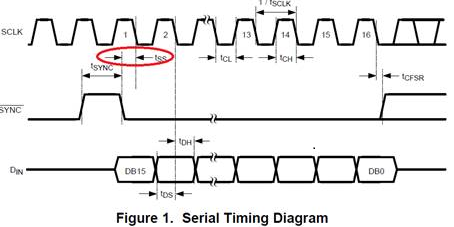

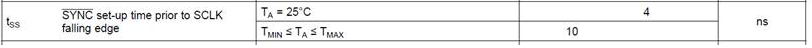

According to Figure 1.(datasheet page 6), SCLK is input before SYNC pulse.

Is SCLK needed before SYNC pulse?

I understand that SPI SCLK is input after CS(SYNC) falling edge generally.

(2)

About SPI mode (CPOL/CPHA),

What mode is supported on DAC084S085?

I think that SPI mode will be mode1(CPHA=1/CPOL=0) from Figure 1.

My understanding is correct?

Regards,

Tao 2199