Other Parts Discussed in Thread: LM1085

Hello,

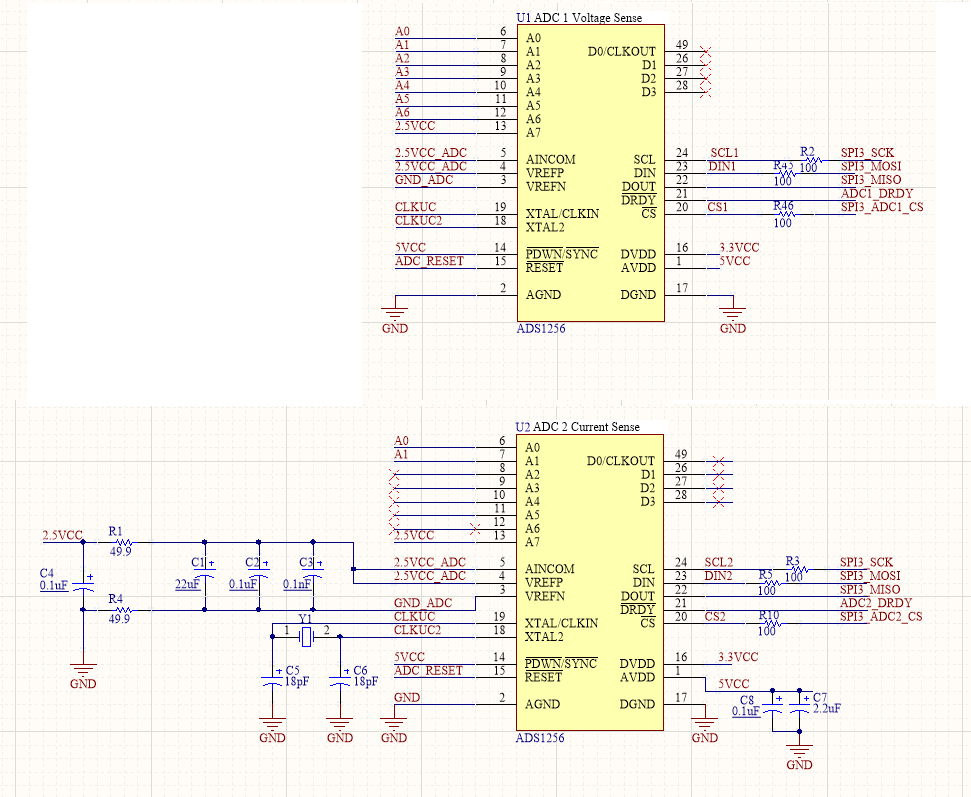

I am currently working on a design that uses two parallel ADS1256 chips to measure signals simultaneously.

The process of two ADCs simultaneously reading is listed below:

1. WREG channel to Mux Reg of both ADCs

2. Send SYNC commands to both ADCs

3. Send WAKEUP commands to both ADCs

4. Wait for DRDY of ADC1 to be low, then send RDATA command to ADC1

5. Wait for DRDY of ADC2 to be low, then send RDATA command to ADC2

Between each process of reading the same channel, there can be 0.2mV reading spike.

As far as the circuit setup goes the ADCs share the same crystal (7.68MHz). The

SPI Bus is shared between the two (chip select and data ready are separated). AIN COM and VREFP are tied to 2.5V and this is also shared between the two ADCs.

sampling rate: 60SPS

Input buffer: Off

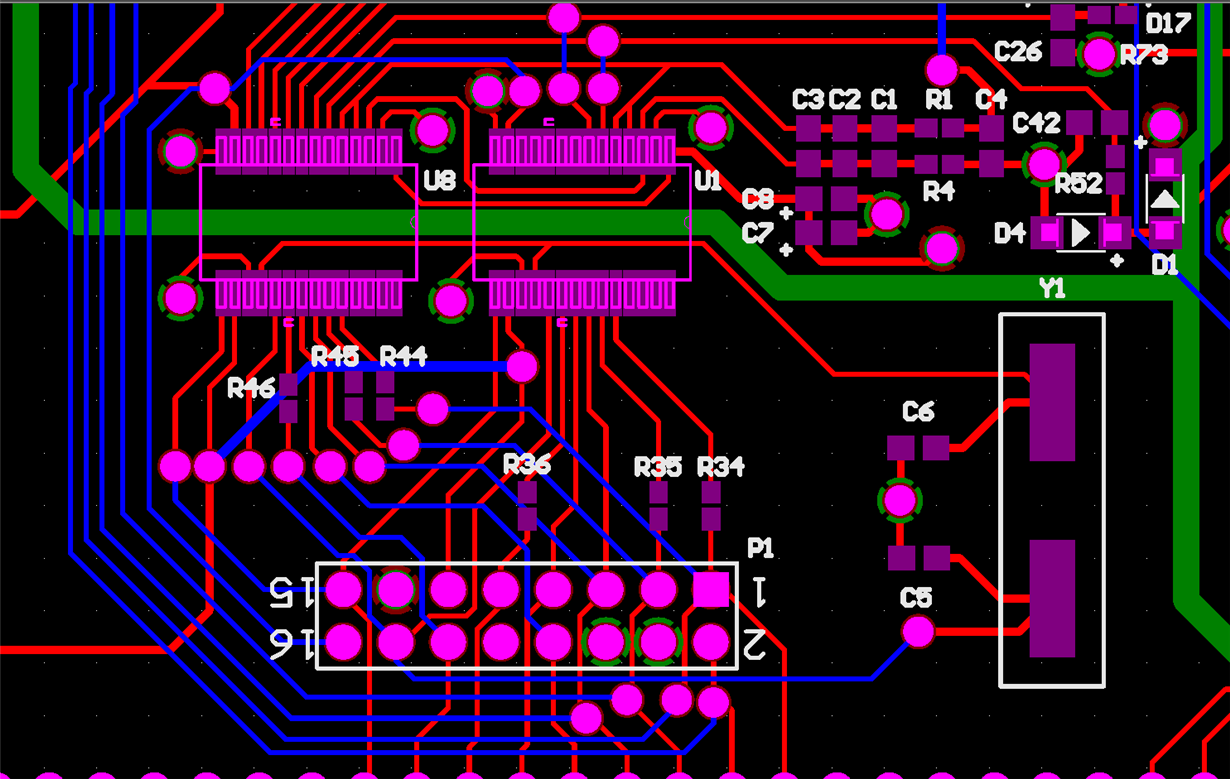

I do have a ground plane split underneath of the two ADCs separating the digital side and the analog side but they tie back together at another section of the PCB. I was wondering if you could provide some advice for minimizing noise while operating two parallel ADCs or specific device considerations that I might have missed?

Thanks for your time,

Mike