Other Parts Discussed in Thread: ADS131E08

I am trying to develop a demo using the ADS131E08EVM-PDK and am noticing that the input seems to be attenuated by a factor of 2. I am also noticing that VREFP doesn't seem to be supplied internally. I think this may be because I am not using the Modular EVM Motherboard and am instead using Test Points 7 and 10 to power the board, so if this setup will cause damage to the board, please let me know.

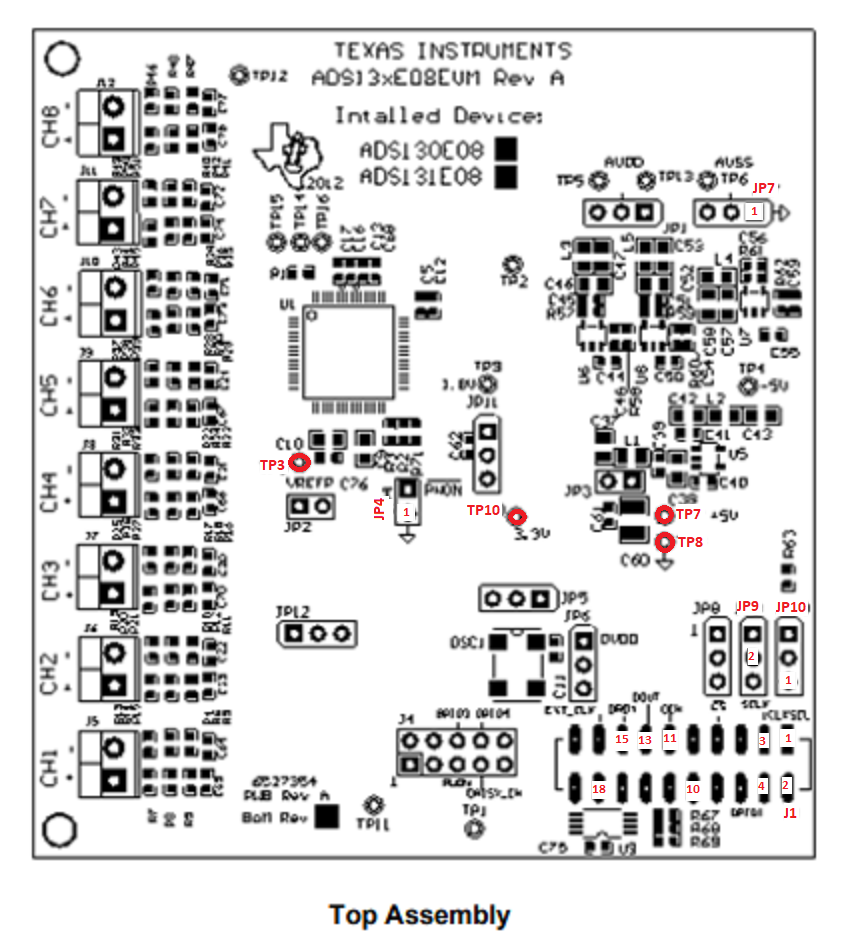

I am using an NI PXIe-4145 to power the board by supplying 5V to TP 7, supplying one power supply low to TP 8 (all power supply grounds are tied internally and are floating), and I am supplying 3.3V to TP 10. To work around the VREFP behavior and some unstable behavior on VREFN, I've supplied 2.5V to TP 3 and -2.5V to TP6 (because AVSS is tied to VREFN). I am also using an NI PXIe-4463 to generate a sine wave (±2.5V) and am feeding it into channel 1 of the EVM. Finally, to acquire the data, I am using an NI PXIe-6570 and am acquring data on the SPI lines. I've attached an image below of my wiring (please forgive the clutter) as well as a simplified image to show which test points and pin headers are being used.

(Pin 2 on the J1 header isn't used, I simply labeled it to make it easier to understand the numbering convention)

The reason I believe the signal supplied is attenuated is because when I feed in a sine wave with an amplitude of 2.5V, the data I receive back scales to a 1.25V sine wave. I've double-checked the signal fed in by supplying a constant 1V and reading back 1V on a DMM. When I read the same signal from the ADC, it's scaled as 0.5V. Also, when I read the raw ADC binary for the 2.5V amplitude sine wave, there is a gap in codes between ~16000 and ~44000, indicating that the signal being read is roughly half of the full scale range.

Finally, one major concern I've had is that after performing constant testing on one ADC, the THD fell out of specification, which made me think I may have damaged the part. I haven't seen the THD fall on a second ADC after minimal testing, but since I briefly saw the correct amplitude read back on the second ADC and then saw it read back an attenuated value about 15 minutes later, I was concerned I was causing damage to the part.

All of that said, I have a few questions:

- Is the setup without the motherboard causing damage to the EVM?

- If the answer to (1) is no, is the motherboard supposed to supply the VREFP internal voltage, and if it is, would it damage the EVM to supply this externally via TP 3?

- If the board isn't being damaged, is there a reason why the signal seems to be attenuated?

- If I must use the motherboard, can I still communicate with the EVM via SPI?

- Not related to problematic behavior, but one thing I was wishing to demonstrate was INL testing. Do you perform the histogram INL method for your tests, or do you use a different method?

If there is any information that is missing, please let me know, and I'll supply whatever I can!