Hello,

I am trying to connect my ADS1258EVM board to a gumstix computer via SPI. I shifted the logical level to 3.3V and connected SCLK, DIN, DOUT and CS. Trying to poll the data i dont think i need any more, do i? START is pulled low, PWDN high.

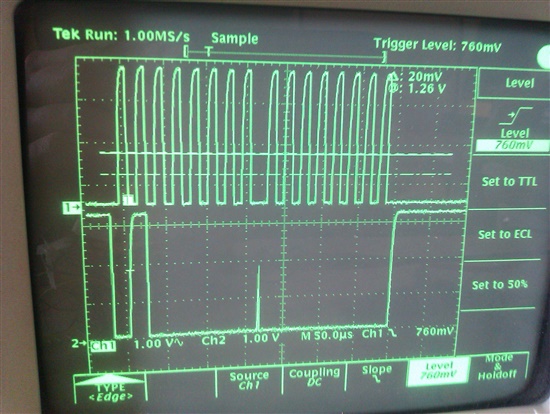

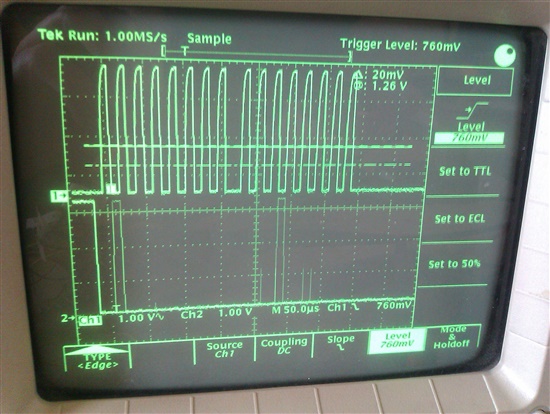

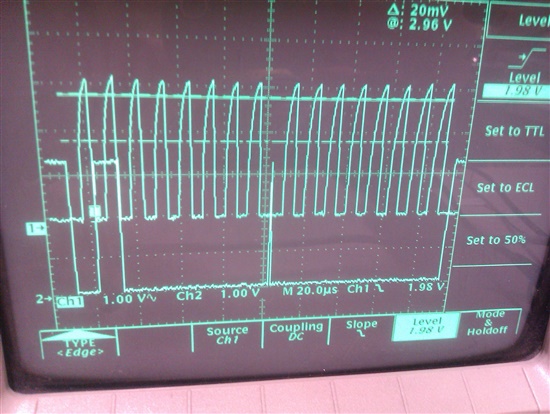

Well, after I did connect everything and i see the correct signal on the scope (unfortunately an analog one, so i cant really send you plots). I am only trying to read the ID Register first, so I send 0x4000 to the ADS1258 and read the second byte in my response buffer.

With a data rate 6400Hz I dont get any response (0x00). Increasing the data rate I get some results which look pretty much random. I cannot exceed the data rate further than approx. 100 000Hz because my level shifters are too slow. I am wondering if this can be a problem with the ADS1258.

I am pretty confident that the ADS1258 does not even understand my request, because i was also sending other commands (register write, data read, data read direct etc.) and only get back random data on DOUT. I am guessing that somehow i am triggering the device to send data, but i am not really sure why this misinterpretation happens.

I would appreciate if you could give me some hints, maybe also how i could debug this error, because i am running out of ideas.

Regards,

Norman