Other Parts Discussed in Thread: TINA-TI, OPA625, , OPA320, THS4551

Tool/software: TINA-TI or Spice Models

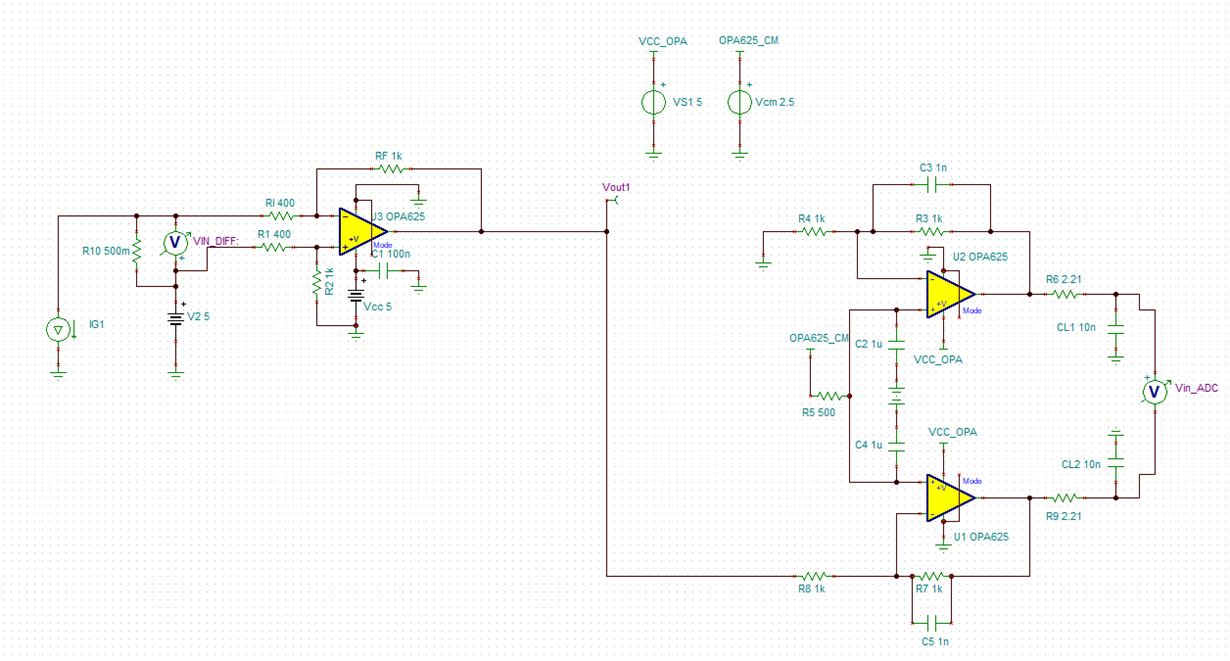

opa625_try.TSCI was tried to use the front end figure 105 shown in the datasheet of ADS8900B.

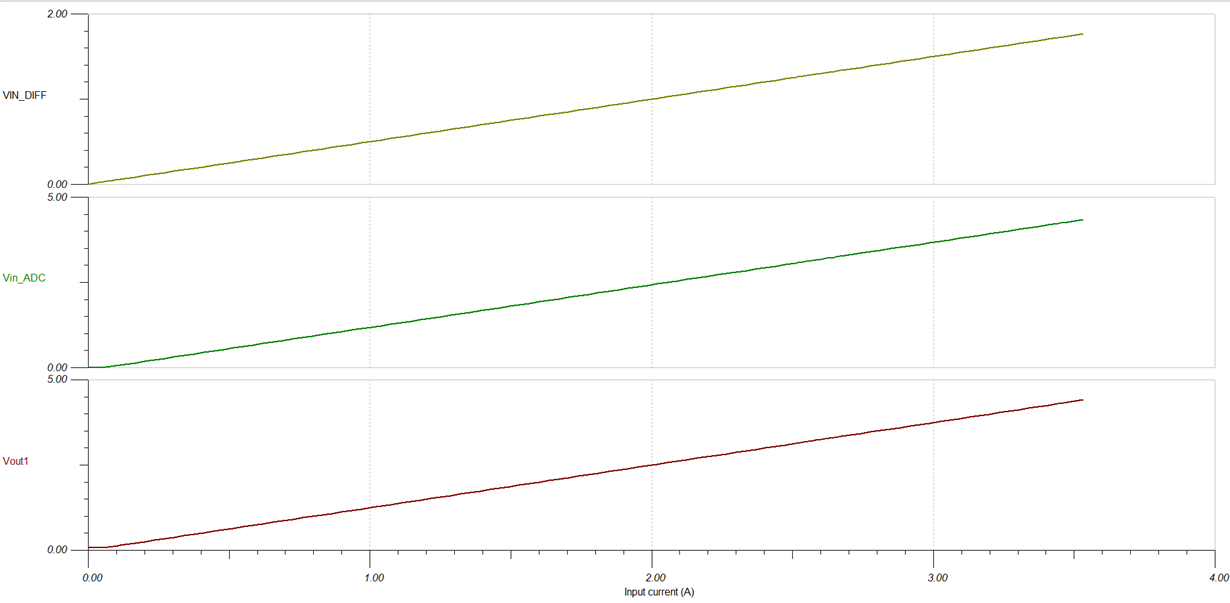

I need to measure the current from 0-3.5A in high side3.3V line in 10uA resolution. so that I chose this ADC[20-bit]. I am going to use 0.5Ohm current sense resistor and plan to measure by the drop of that resistor. I simulated this front end in Tina-TI as per the Figure i mentioned above. it gives very good response in the simulation and the changes for every 10uA also linearly changing in the simulation.

Since the reference voltage of ADC is starts from 2.5V, I need to map the resistor drop into full scale voltage, so I need gain amplifier. My input signal frequency may go upto MHz, so i need high bandwidth. so that i plan to use the same op-amp OPA625 For gain amplifier. I designed basing differential amplifier using this part and given the output to the front end of the ADC. the output is good but after few amperes say 50mA. This much initial amperes i cannot compromised. I need to avoid such limitations.

Can you please verify my design and suggest any modification?

And I need to measure the current from 0-3.5A by 0.5A resistor (resistor drop range 0-1.75V). The full scale mentioned in datasheet is -Vref to +Vref but I need to map this resistor drop to this full scale value. Can you please suggest configuration tips? or can I use the configuration shown in the figure 111 in dataheet of ADC?

Here I attached the Tina Schematic design

Output waveform(Notify initial few mA upto 50mA. the output is not started)