Hello guys,

I designed a Data Acquisition system with ADS131e08 ADC and spartan6 FPGA.

I config the ADC and read data from it by my vhdl code that it contains several States. In this states, the ADC first reset and then the Config registers sets correctly.

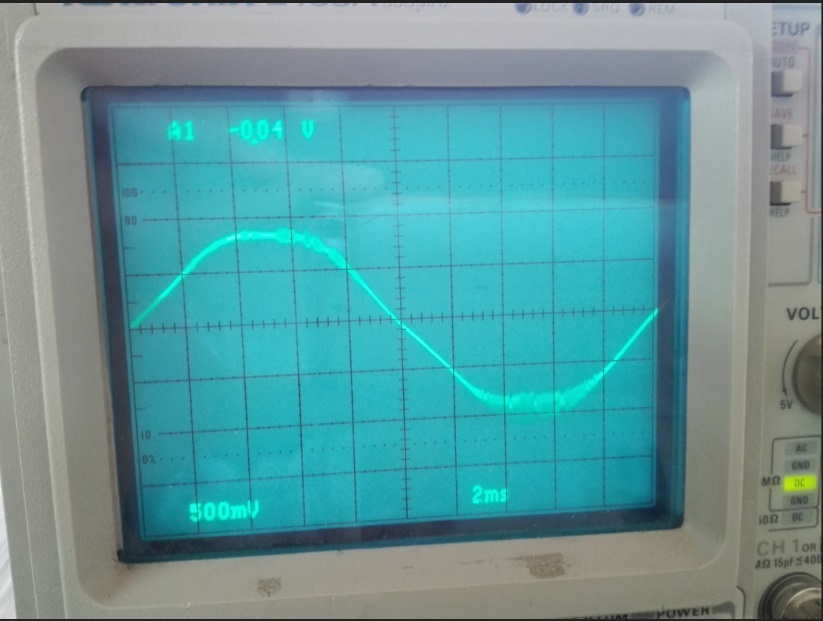

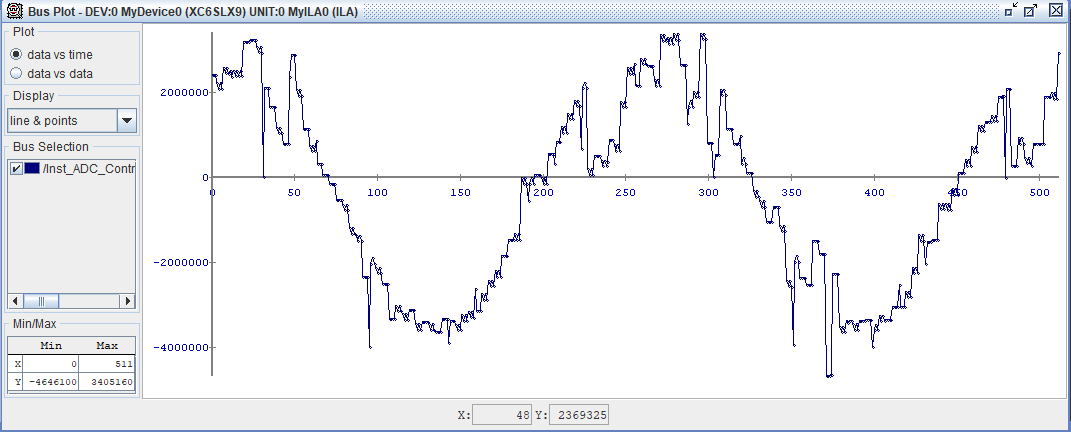

I use xilinx Chipscope to capture the received data. when the Analog input of ADC is set to DC values, the received data in chipscope is correct and no problems, but when analog input connected to AC value(sine wave), the received data is not sine.

I set the ADC parameters to:

Fclk= 2.048 MHz

Fsclk = 18.432 MHz

Fchipscope= 2* Fsclk

Data Rates : 1KSPS

RESOLUTION = 24bit

AVDD = +2.5v

AVSS = -2.5v

sine Wave (peek to peek = 4v) that is less than the ADC Vp-p = AVDD - AVSS.

I guess the problem is related to the Chipscope settings?Rights?

Please help me to solve this problem.

regards,

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.