Other Parts Discussed in Thread: TMS320C203

The TLV5614's rev B datasheet does nor address the LDAC* pin's timing requirements. Can some insight be provided?

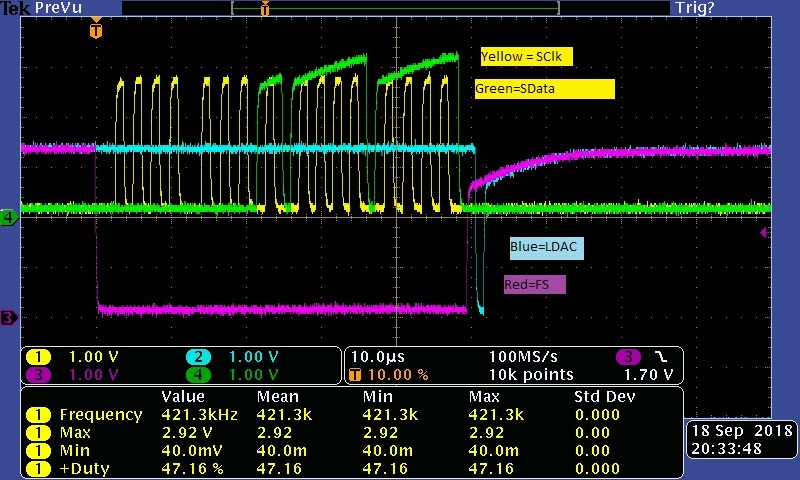

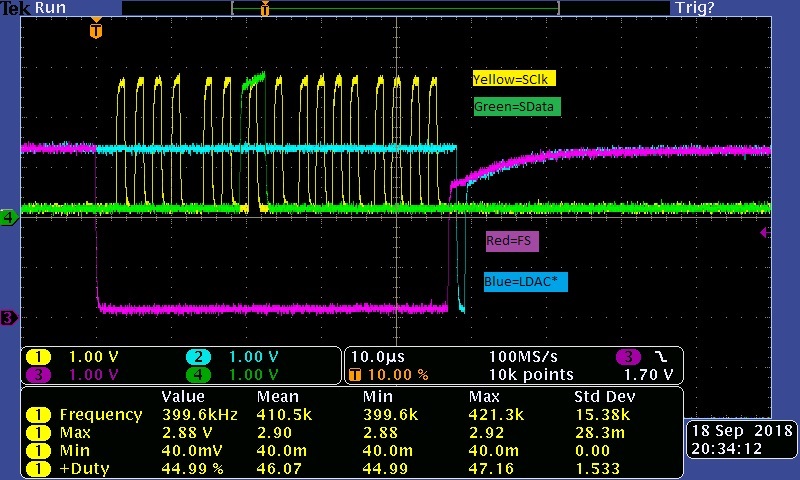

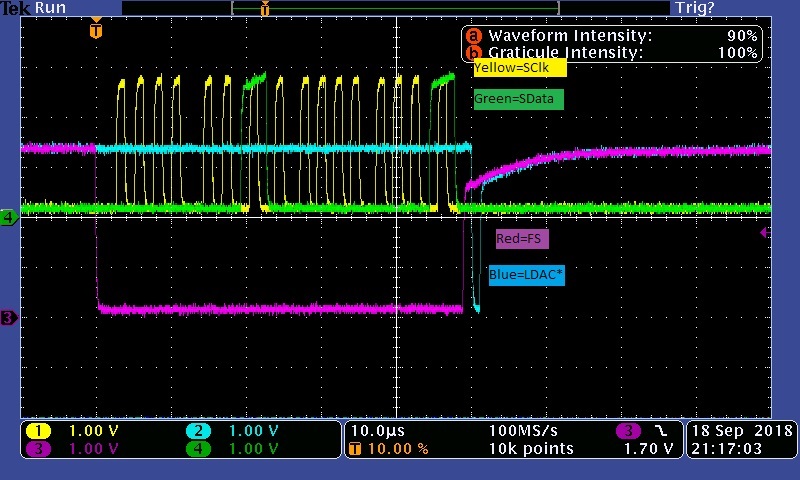

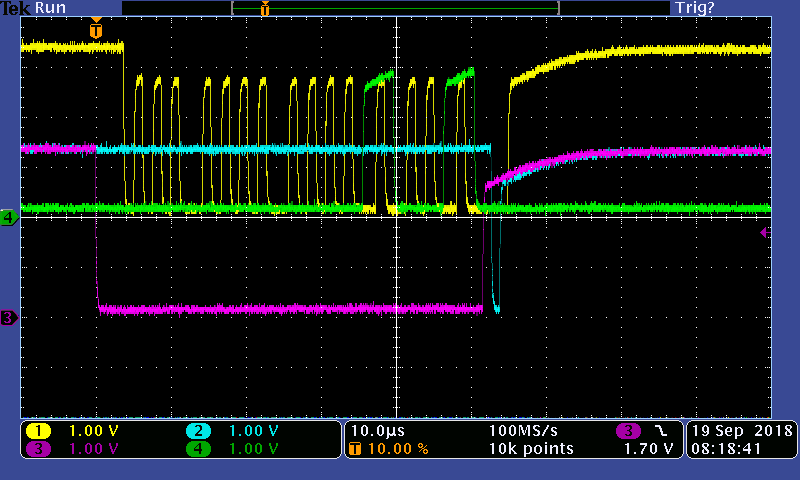

Background I'm having issues with the output updating consistently. Seems to update every other time.

I'm following the datasheet timing requirements to load the register, which are:

CS* low, then FS low. Then load 16 bits while both CS* and FS low. Then FS hi.

After this (update of the input register), pulse LDAC* low. The delay (after FS hi before pulsing LDAC* lo) = ~1us, and LDAC* is low for ~1us before returning LDAC* HI.

Any specs or suggestions?