To whom Related,

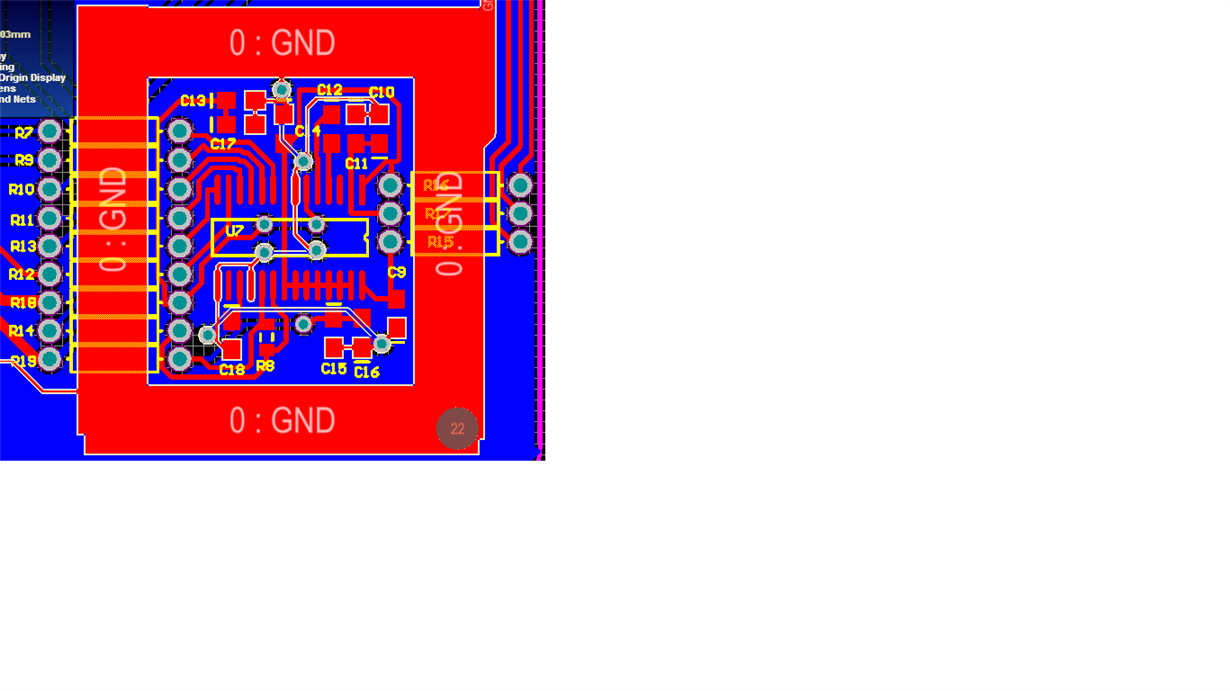

My name is celal. My circuit is included in ads1262, analog gyroscope(adxrs624) and esp8266 arduino board. Connections and pcb layout of ads1262 as attached. I use a generic codes from this forum as below.

ads1262_Reg_Write(POWER, 0x11);delay(10); //11h (default) internal ref enabled

ads1262_Reg_Write(INTERFACE, 0x0D);delay(10); //05h (default) Status byte enabled, Checksum enablade

ads1262_Reg_Write(MODE0, 0x00);delay(10); //00h (default) Continuous Conv Mode | 0x40 Pulse conversion mode (one shot conversion)

ads1262_Reg_Write(MODE1, 0x00);delay(10); //80h (default) FIR Filter | 00h sinc1 | 60h sinc4

ads1262_Reg_Write(MODE2, 0x89);delay(10); //04h (default) PGA enabled 1V/V 20sps| 5Ch 32V/V 7200sps | 5Fh 32V/V 38400sps

ads1262_Reg_Write(INPMUX, 0xEE);delay(10); //01h (default) Multiplexer, AIN0 e AIN1 | 23h AIN2 e AIN3

ads1262_Reg_Write(OFCAL0, 0x00);delay(10); //00h (default) Offset Calibration Registers

ads1262_Reg_Write(OFCAL1, 0x00);delay(10); //00h (default) Offset Calibration Registers

ads1262_Reg_Write(OFCAL2, 0x00);delay(10); //00h (default) Offset Calibration Registers

ads1262_Reg_Write(FSCAL0, 0x00);delay(10); //00h (default) Full-Scale Calibration Registers

ads1262_Reg_Write(FSCAL1, 0x00);delay(10); //00h (default) Full-Scale Calibration Registers

ads1262_Reg_Write(FSCAL2, 0x40);delay(10); //40h (default) Full-Scale Calibration Registers

ads1262_Reg_Write(IDACMUX, 0xBB);delay(10); //BBh (default) Output Multiplexer, no connection, no connection

ads1262_Reg_Write(IDACMAG, 0x00);delay(10); //00h (default) Current magnitude, off

ads1262_Reg_Write(REFMUX, 0x00);delay(10); //00h (default) Reference Multiplexer, 2.5V, 2.5V

ads1262_Reg_Write(TDACP, 0x00);delay(10);//00h (default) TDACP, no connection

ads1262_Reg_Write(TDACN, 0x11);delay(10); //00h (default) TDACN, no connection

ads1262_Reg_Write(GPIOCON, 0x00);delay(10); //00h (default) GPIO not connected

ads1262_Reg_Write(GPIODIR, 0x00);delay(10); //00h (default) GPIO output

ads1262_Reg_Write(GPIODAT, 0x00);delay(10); //00h (default) GPIO low

ads1262_Reg_Write(ADC2CFG, 0x00);delay(10); //00h (default) ADC2

ads1262_Reg_Write(ADC2MUX, 0x01);delay(10); //01h (default)

ads1262_Reg_Write(ADC2OFC0, 0x00);delay(10); //00h (default)

ads1262_Reg_Write(ADC2OFC1, 0x00);delay(10); //00h (default)

ads1262_Reg_Write(ADC2FSC0, 0x00);delay(10); //00h (default)

ads1262_Reg_Write(ADC2FSC1, 0x40);delay(10); //40h (default)

SPI.transfer(START);

I selected test dac to analog inputs like positive is 2.5V and negative is 2.4921875V as per at the datasheet.The difference is about 7.8125 mV. I got result from 7.84 mV to 8.15 mV. simple span=((8.15-7.84)/(8.15+7.84)/2)*100=4%

I expected 0.4%of simple span but adc output ten times grater than expected.

Can you suggest any tips or tricks about improve the result?