Part Number: ADS4149

Other Parts Discussed in Thread: ADS54J40, ADS54J40EVM, ADS54J60, ADS41B49, , LMK04821, LMK04208, LMK04828

Dear Specialists,

My customer is considering a system of 14 to 16 bits and 1Gsps.

I would be grateful if you could advise.

---

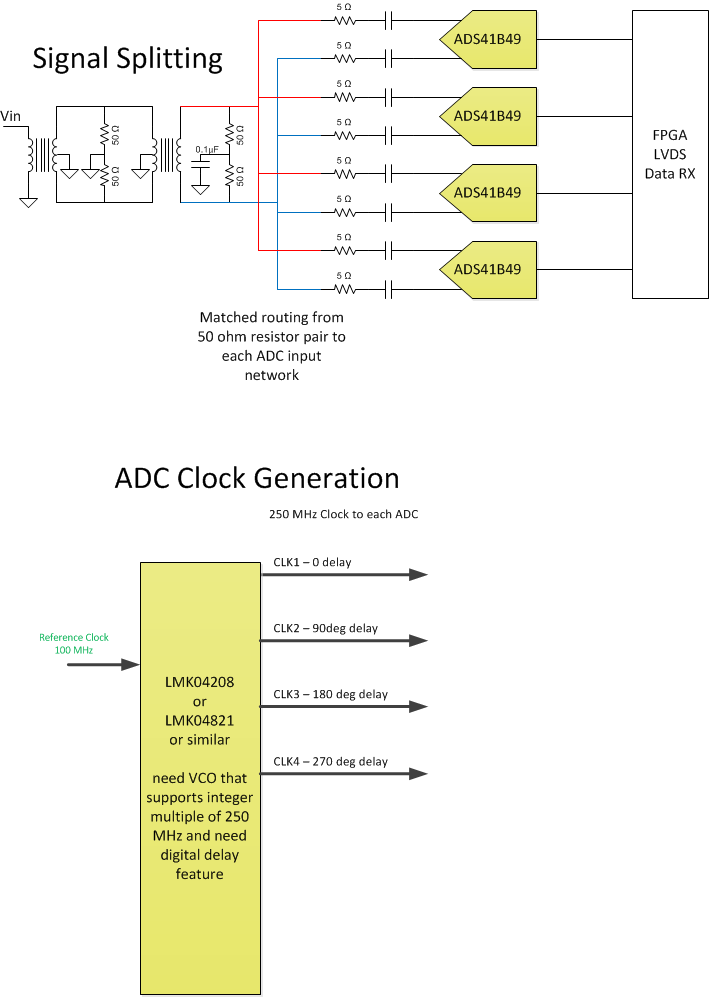

There is a demand for realization with a parallel ADC because there is a limitation in the production of the substrate.

I'd like to use Interleave like SLAU247, are there any reference designs that match the above conditions?

To realize 1 Gsps, I think that four 250 Msps devices will be used.

I would like you to propose it together with the A / D converter.

---

I appreciate your great help in advance.

Best regards,

Shinichi