I have an application in which the ADS1120 is being used in the following manner. A piezoresistive bridge is excited by the 0.5mA IDAC source and read differentially between AIN0 and AIN1. Two trimmer pots are read on AIN2 and AIN3.

The SPI lines are being driven by a STM32L011.

I have an issue setting the configuration registers. No matter what I write to the registers, the readback values are 0xFF or 0x00.

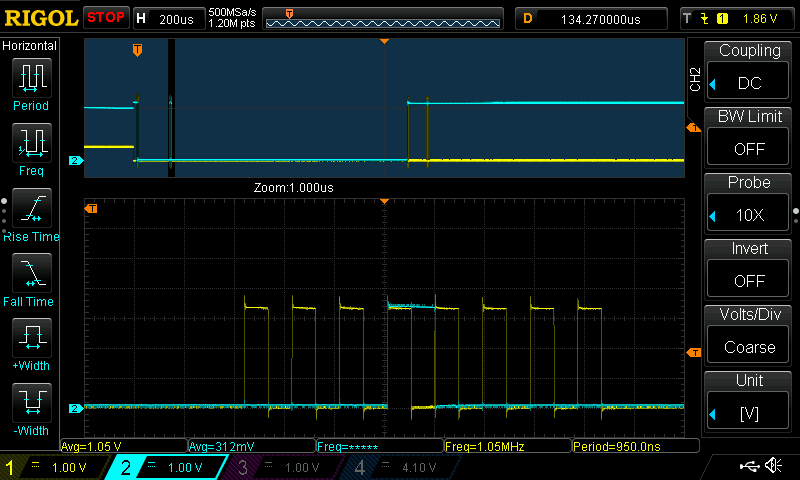

Furthermore, if I attempt to issue a RDATA command as shown by the following capture of MOSI and SCK

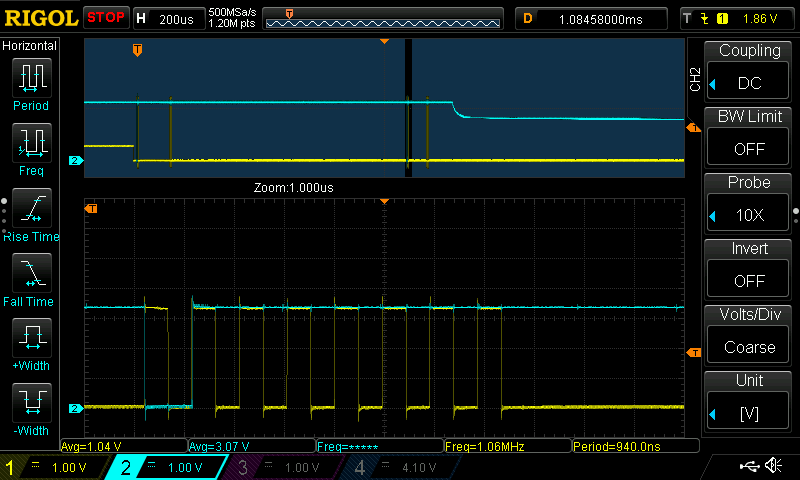

the next two bytes that I read are always 0x7F, 0xFF like in the following capture of MISO and SCK

I can see that the SPI line transitions on MOSI, MISO and SCK are sharp without much overshoot or undershoot. Furthermore, the ADS1120 seems to be clocking out something, since the first byte is always 0x7F.

I have verified that are no dips or brownouts on either AVDD or DVDD pins and GND connections of both pins have less than 0.1 Ohm impedance to the ground plane.

I have racked my brains trying to think of a reason why this could be happening, since the chip worked perfectly in my last iteration of the design. All that's changed between the iterations is that the four 47 Ohm resistors are moved to the bottom plane with vias to the top plane on either side adjacent to the corresponding pins on the microcontroller and ADS1120.

I would be very grateful for any advice anyone could offer me.

Thanks in advance,

Gaurav.