Part Number: ADS7883

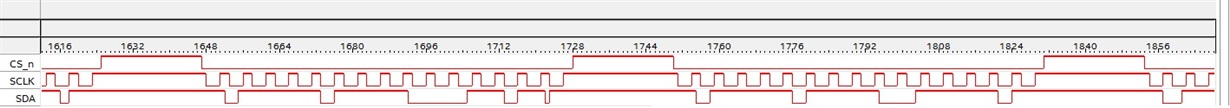

SPI signals which I sampled from ADS7883 component in my board, are attached above.

Above the signals there is a ruler with numerated ticks.

The time between each two adjacent ticks is 1/75Mhz. The SCLK is spread over 5 ticks. So it means that SCLK frequency that I use is 15Mhz.

I don't understand 3 things:

1. According to the datasheet ADS7883 is supposed to output on its SDA output 16 bits on each reading cycle.

According to the datasheet the first 2 bits (of the 16 bits) are always zero

So why is the first bit = ‘1’ on each reading cycle (as seen in the sampled signals above)?

2. According to the datasheet the last 2 bits (of the 16 bits) are always zero.

So why is one of the 2 last bits on each reading cycle (as seen in the sampled signals above) different from ‘0’?

3. Why do I get the short zero on SDA signal on tick number 1722?

I don’t understand how the data (of SDA) can be shorter than the SCLK.

Waiting for answers

Regards

Zvi