Other Parts Discussed in Thread: ADS54J60, LMK04828, , ADS54J69

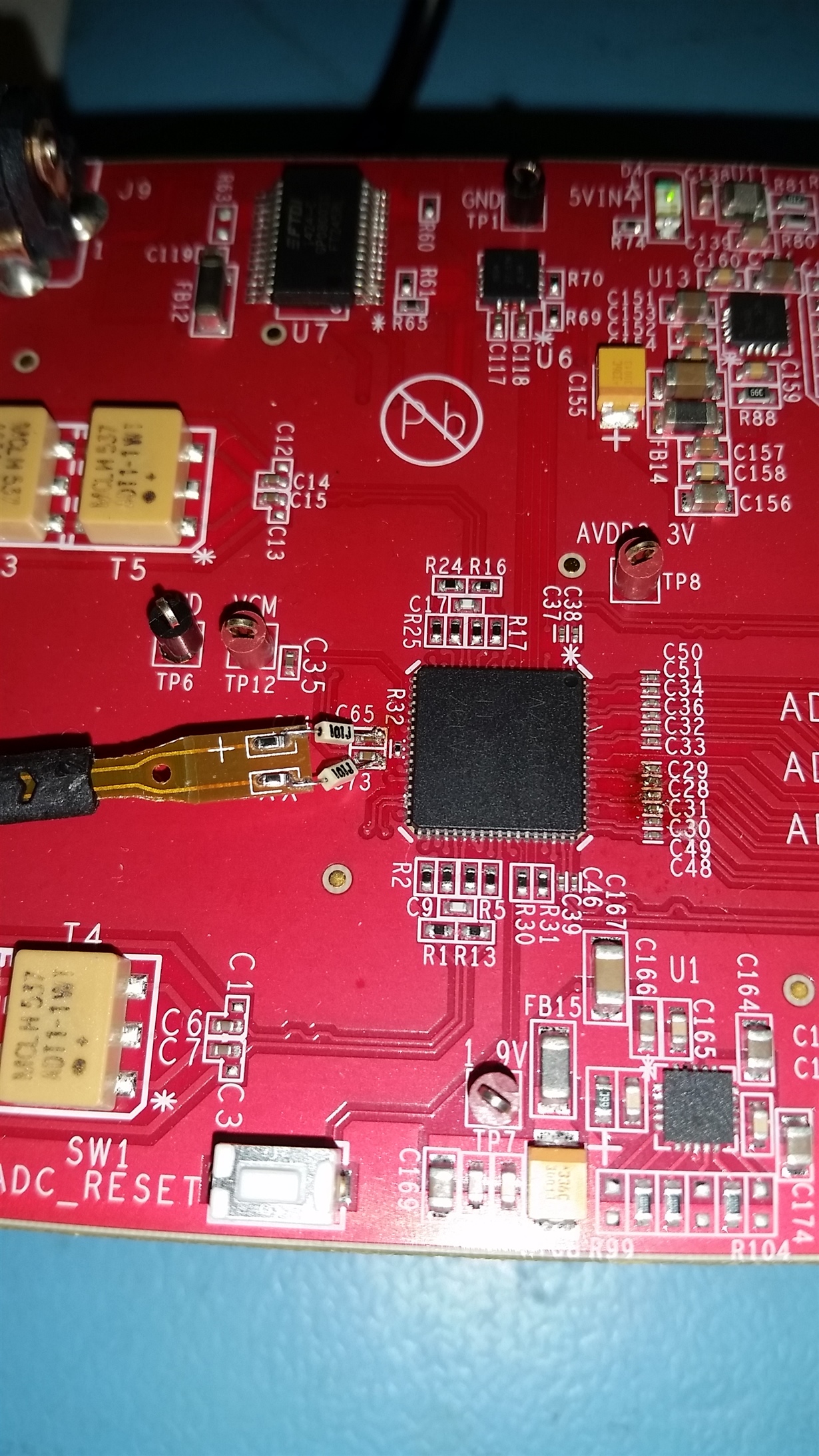

We are currently evaluating the ADS54J60 for a project and need the possibility to move the sampling phase of the ADC relative to the FPGA (there are several ADCs, each with an individual sampling delay).

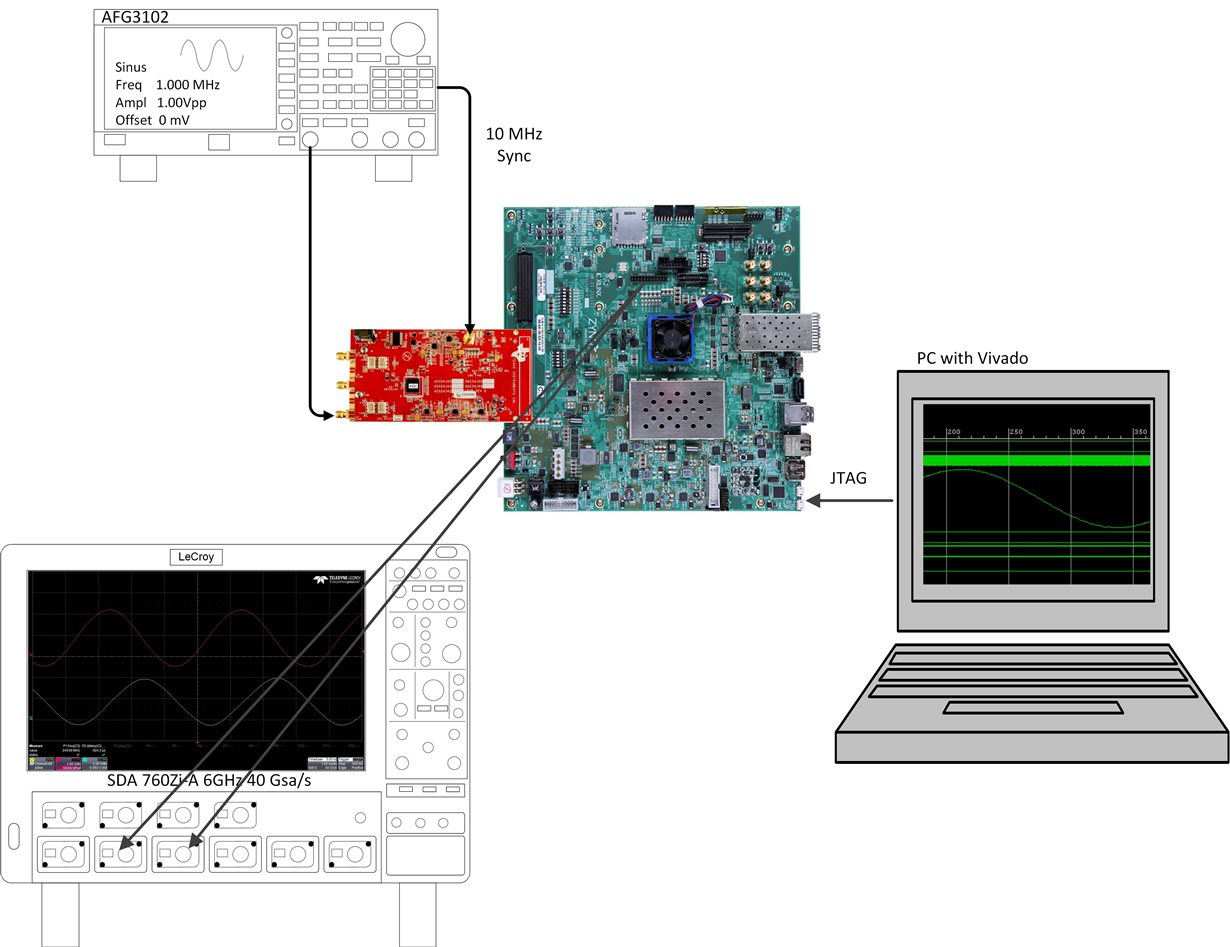

The ADC data is sampled at 500 MSa/s @ 16 bit = 8 Gbit/s => using 8B/10B of JESD204B ends up to be 10 GSa/s and routed to an ZCU102 Board of Xilinx on the FMC connector routed to the Zynq Ultrascale+ MPSoC FPGA.

I see the system working properly and check the data from the ADC using an integrated logic analyzer (ILA) of Xilinx and see clean and proper data.

Now I start moving on the eval board the clock distribution chip LMK04828, the output DCLK 2, the analog delay, in steps of 25 ps. I'm able to observe the phase shift with an oscilloscope between the reference clock and the recovered clock from the FPGA... hence this part is working as it should.

At about 950 ps analog delay the FPGA is not able to lock anymore on the ADC data and delivers lots of crap. Will say not even the K28.5 is sampled anymore correctly.

Now my question_ Did anyone ever try to move the sampling phase of the ADC successfully using the JESD204B interface? In theory this should be possible, since the FPGA MGTs run with slightly different frequencies hence I would have expected that it is as well possible with a JESD204B... especially since I'm only sending K25.5 characters which is used to align the symbols.

Cheers

Goran