Hi,

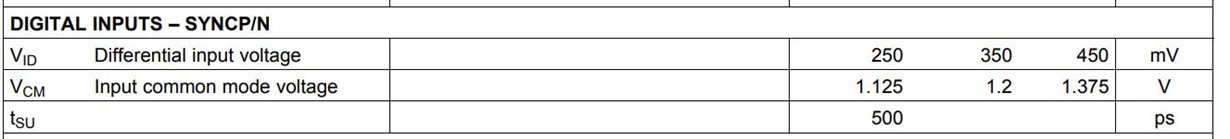

SYNC pin voltage range is specified as below.

Though my customer send sync signal from FPGA, voltage range is not match as below;

FPGA LVDS Spec(1) Vodiff :247mV(min),350mV(typ),600mV(max)

FPGA LVDS Spec(2) Vocm :1.0V(min),1.25V(typ),1.425V(max)

Have looked for TI's LVDS buffer, I could not find the product satisfied with above input specification.

Do you have any idea to solve it?

Best Regards,

Kuramochi