Hi,

My customer is evaluating ADS52J90 on their pre-production.

They use multiple ADS52J90 chips and try to synchronize chips.

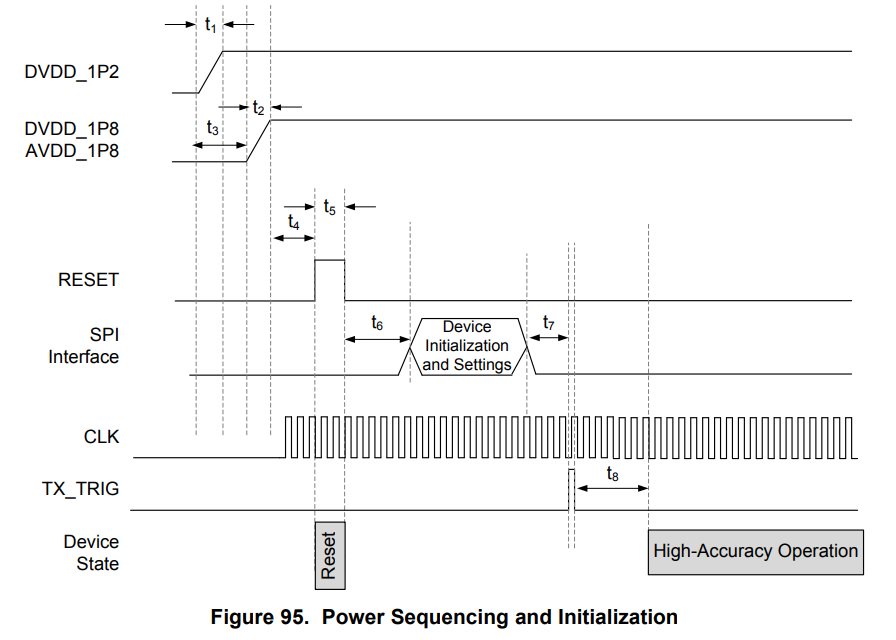

However, synchronization error sometimes occur at about 0℃, and it improves when below t4~t8 become longer than typical condition(they are 10 times of min value).

Though t4~t8 seem to be related to chip synchronization, is it correct understanding?

If no, why is synchronization error improved by changing power sequence?

We would like to know if changing power sequence is correct as workaround of synchronization error.

Best Regards,

Kuramochi